|

|

PDF HSP50214A Data sheet ( Hoja de datos )

| Número de pieza | HSP50214A | |

| Descripción | Programmable Downconverter | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HSP50214A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

HSP50214A

[ /Title

(HSP5

0214A

)

/Sub-

ject (

Pro-

gram-

mable

Down-

con-

verter)

/Autho

r ()

/Key-

words

(Inter-

sil

Semi-

con-

ductor,

Down-

con-

verter,

Down

Con-

verter,

Pro-

gram-

mable

Down-

con-

verter,

DSP,

AMPS,

TDMA

, North

Ameri-

can

December 1999

Features

POSSOIBBLSEOSLHUESBTPSE5T0PIT2RU1O4TDBEUPCRTODUCT

Programmable Downconverter

Description

• Up to 65 MSPS Front-End Processing Rates (CLKIN) and

55 MSPS (41 MSPS Using the Discriminator) Back-End

Processing Rates (PROCCLK)

Clocks May Be Asynchronous

• Processing Capable of >100dB SFDR

• Up to 255-Tap Programmable FIR

• Overall Decimation Factor Ranging from 4 to 16384

• Output Samples Rates to ≅12.94 MSPS with Output Band-

widths to ≅ 982kHz Lowpass

• 32-Bit Programmable NCO for Channel Selection and Car-

rier Tracking

• Digital Resampling Filter for Symbol Tracking Loops and

Incommensurate Sample-to-Output Clock Ratios

• Digital AGC with Programmable Limits and Slew Rate to

Optimize Output Signal Resolution; Fixed or Auto Gain

Adjust

• Serial, Parallel, and FIFO 16-Bit Output Modes

• Cartesian to Polar Converter and Frequency Discriminator

for AFC Loops and Demodulation of AM, FM, FSK, and

DPSK

• Input Level Detector for External I.F. AGC Support

Applications

• Single Channel Digital Software Radio Receivers

• Base Station Rx’s: AMPS, NA TDMA, GSM, and CDMA

• Compatible with HSP50210 Digital Costas Loop for PSK

Reception

• Evaluation Platform Available

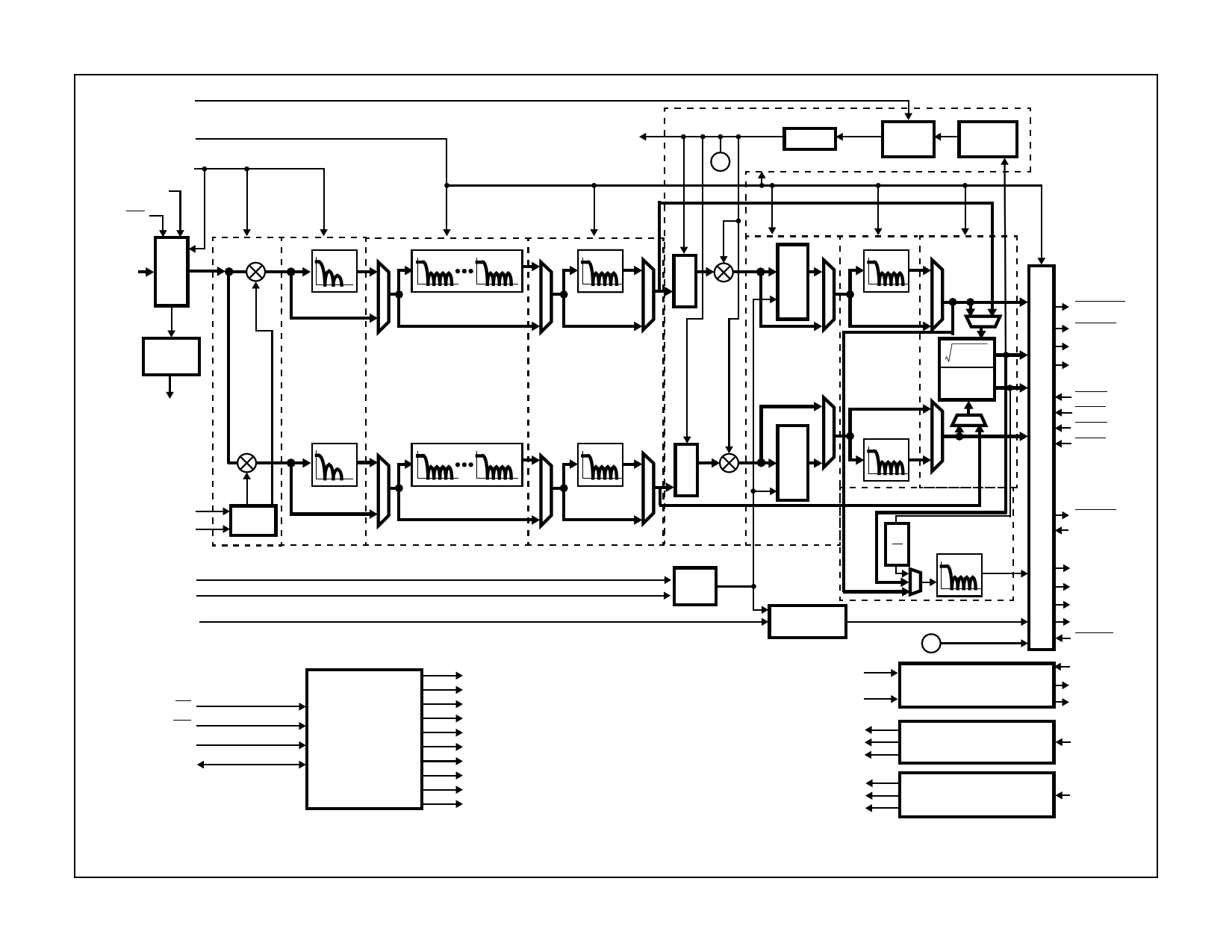

The HSP50214A Programmable Downconverter converts dig-

itized IF data into filtered baseband data which can be pro-

cessed by a standard DSP microprocessor. The

Programmable Downconverter (PDC) performs down conver-

sion, decimation, narrowband low pass filtering, gain scaling,

resampling, and Cartesian to Polar coordinate conversion.

The 14-bit sampled IF input is down converted to baseband

by digital mixers and a quadrature NCO, as shown in the

Block Diagram. A decimating (4 to 32) fifth order Cascaded

Integrator-Comb (CIC) filter can be applied to the data

before it is processed by up to 5 decimate-by-2 halfband fil-

ters. The halfband filters are followed by a 255-tap pro-

grammable FIR filter. The output data from the

programmable FIR filter is scaled by a digital AGC before

being re-sampled in a polyphase FIR filter. The output sec-

tion can provide seven types of data: Cartesian (I, Q), polar

(R, q), filtered frequency (dq/dt), Timing Error (TE), and

AGC level in either parallel or serial format.

Ordering Information

PART

NUMBER

TEMP.

RANGE (oC)

PACKAGE

HSP50214AVC 0 to 70 120 Ld MQFP

HSP50214AVI -40 to 85 120 Ld MQFP

PKG. NO.

Q120.28x28

Q120.28x28

Block Diagram

C(7:0)

IN(13:0)

GAIN

ADJ

(2:0)

COF

SOF

CLKIN

PROCCLK

REFCLK

MICROPROCESSOR

READ/WRITE

CONTROL

LEVEL DETECT

5TH

ORDER

CIC

FILTER

CARRIER

NCO

5TH

ORDER

CIC

FILTER

RESAMPLING

NCO

AGC LOOP FILTER

AGC

POLYPHASE

FIR AND

HALFBAND

FILTERS

POLYPHASE

FIR AND

HALFBAND

FILTERS

I OUT

CARTESIAN

TO

POLAR

COORDINATE

CONVERTER

MAG.

PHASE

Q OUT

FREQ

DISCRIMINATOR

TIMING ERROR

∆

SEROUTA

SEROUTB

AOUT(15:0)

BOUT(15:0)

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

1

File Number 4449.1

1 page

AGCGNSEL

PROCCLK

CLKIN

GAINADJ(2:0)

ENI

TO OUTPUT FORMATTER

AND MICROPROCESSOR

INTERFACE

AGCOUT

A

IN(13:0)

LEVEL

DETECT

TO

µPROCESSOR

INTERFACE

MIXER

5TH ORDER

CIC

DECIMATE

FROM 4-32

0 TO 5 HALFBAND FILTER;

DECIMATION UP TO 32

(CO = 1;

Cn = 0)

255-TAP

PROGRAMMABLE

FIR FILTER

(DECIMATE UP TO 16)

AGC

LIMIT

LOOP

FILTER

ERROR

DETECT

CARTESIAN

TO

POLAR

I

RE-SAMPLER

INTERPOLATE

BY 2/4

HALFBAND

FILTERS

I2 + Q2

atan

Q--I--

Q

COF

COFSYNC

NCO

(CARRIER TRACKING)

SOF

SOFSYNC

REFCLK

MICROPROCESSOR

READ/WRITE

RD

WR

A(2:0)

C(7:0)

CONTROL

SECTION

(CO = 1;

Cn = 0)

(SYMBOL TRACKING)

NCO

OUTPUT SECTION

DISCRIMINATOR SECTION

INPUT SECTION

LEVEL DETECT SECTION

SYNCHRONIZATION SECTION

CARRIER NCO SECTIONS

CIC, HALFBAND FILTER, AND FIR SECTIONS

DIGITAL AGC SECTION

RE-SAMPLER/INTERPOLATION HALFBAND SECTION

TIMING NCO

DISCRIMINATOR

63-TAP

dθ PROGRAMMABLE

dt FIR FILTER

DIFFERENCE

CLKIN

PROCCLK

TIMING ERROR

AGCOUT

A

CHIP

SYNCHRONIZATION

CIRCUITRY

BACK END

SYNCHRONIZATION

CIRCUITRY

FRONT END

SYNCHRONIZATION

CIRCUITRY

FIGURE 1. FUNCTIONAL BLOCK DIAGRAM OF THE HSP50214A PROGRAMMABLE DOWNCONVERTER

DATARDY

INTRRP

AOUT(15:0)

BOUT(15:0)

OEAH

OEAL

OEBH

OEBL

INTRRP

SEL(2:0)

SEROUTA

SEROUTB

SERCLK

SERSYNC

SEROE

MSYNCI

SYNCOUT

MSYNCO

SYNCIN2

SYNCIN1

5 Page

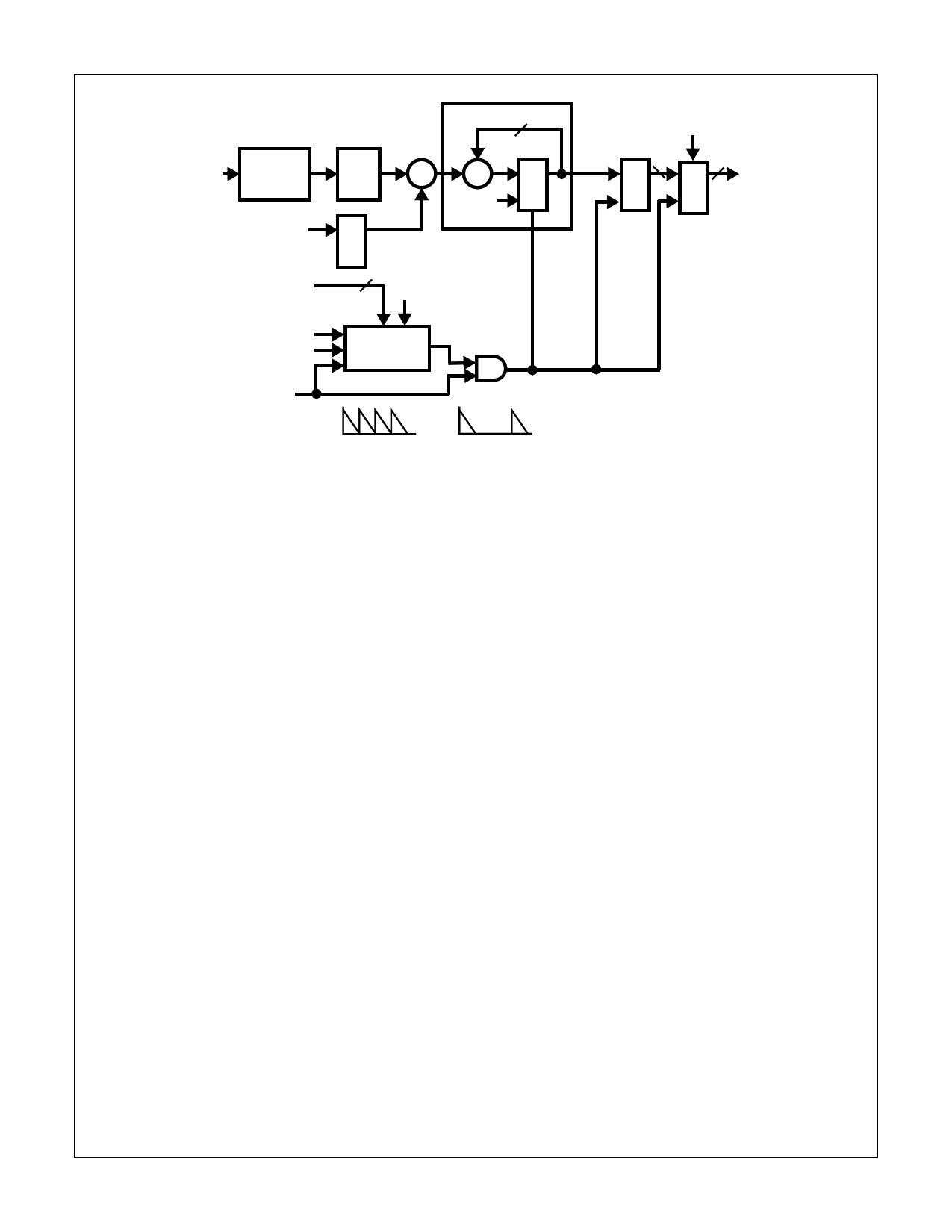

HSP50214A

IN(13:0)

INPUT

GATING

LOGIC

INPUT_THRESHOLD †

INTEGRATION_INTERVAL†

START †

INTEGRATION_MODE †

|X| +

R

E

G

16 “0”

ACCUMULATOR

32

+

CLKIN

R

E

G

COUNTER

CLKIN

† Controlled via microprocessor interface. CONTINUOUS

SINGLE

FIGURE 9.

ADDR(2:0)

R

24

M

TO

E U 8 µPROC

GX

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HSP50214A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HSP50214A | Programmable Downconverter | Intersil Corporation |

| HSP50214AVC | Programmable Downconverter | Intersil Corporation |

| HSP50214AVI | Programmable Downconverter | Intersil Corporation |

| HSP50214B | Programmable Downconverter | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |