|

|

PDF SI8635 Data sheet ( Hoja de datos )

| Número de pieza | SI8635 | |

| Descripción | Low-Power Triple-Channel Digital Isolators | |

| Fabricantes | Silicon Laboratories | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SI8635 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Si8630/31/35 Data Sheet

Low-Power Triple-Channel Digital Isolators

Silicon Lab's family of ultra-low-power digital isolators are CMOS devices offering sub-

stantial data rate, propagation delay, power, size, reliability, and external BOM advantag-

es over legacy isolation technologies. The operating parameters of these products re-

main stable across wide temperature ranges and throughout device service life for ease

of design and highly uniform performance. All device versions have Schmitt trigger inputs

for high noise immunity and only require VDD bypass capacitors.

Data rates up to 150 Mbps are supported, and all devices achieve propagation delays of

less than 10 ns. Enable inputs provide a single point control for enabling and disabling

output drive. Ordering options include a choice of isolation ratings (2.5, 3.75 and 5 kV)

and a selectable fail-safe operating mode to control the default output state during power

loss. All products are safety certified by UL, CSA, VDE, and CQC, and products in wide-

body packages support reinforced insulation withstanding up to 5 kVRMS.

Applications

• Industrial automation systems

• Medical electronics

• Hybrid electric vehicles

• Isolated switch mode supplies

• Isolated ADC, DAC

• Motor control

• Power inverters

• Communications systems

Safety Regulatory Approvals

• UL 1577 recognized

• Up to 5000 VRMS for 1 minute

• CSA component notice 5A approval

• IEC 60950-1, 61010-1, 60601-1 (reinforced insulation)

• VDE certification conformity

• Si863xxT options certified to reinforced VDE 0884-10

• All other options certified to IEC 60747-5-5 and reinforced 60950-1

• CQC certification approval

• GB4943.1

KEY FEATURES

• High-speed operation

• DC to 150 Mbps

• No start-up initialization required

• Wide Operating Supply Voltage

• 2.5–5.5 V

• Up to 5000 VRMS isolation

• Reinforced VDE 0884-10, 10 kV surge-

capable (Si863xxT)

• 60-year life at rated working voltage

• High electromagnetic immunity

• Ultra low power (typical)

5 V Operation

• 1.6 mA per channel at 1 Mbps

• 5.5 mA per channel at 100 Mbps

2.5 V Operation

• 1.5 mA per channel at 1 Mbps

• 3.5 mA per channel at 100 Mbps

• Tri-state outputs with ENABLE

• Schmitt trigger inputs

• Selectable fail-safe mode

• Default high or low output (ordering

option)

• Precise timing (typical)

• 10 ns propagation delay

• 1.5 ns pulse width distortion

• 0.5 ns channel-channel skew

• 2 ns propagation delay skew

• 5 ns minimum pulse width

• Transient Immunity 50 kV/µs

• AEC-Q100 qualification

• Wide temperature range

• –40 to 125 °C

• RoHS-compliant packages

• SOIC-16 wide body

• SOIC-16 narrow body

silabs.com | Smart. Connected. Energy-friendly.

Rev. 1.6

1 page

Si8630/31/35 Data Sheet

Device Operation

3. Device Operation

Device behavior during start-up, normal operation, and shutdown is shown in Figure 3.1 Device Behavior during Normal Operation on

page 6, where UVLO+ and UVLO– are the respective positive-going and negative-going thresholds. Refer to the following tables to

determine outputs when power supply (VDD) is not present and for logic conditions when enable pins are used.

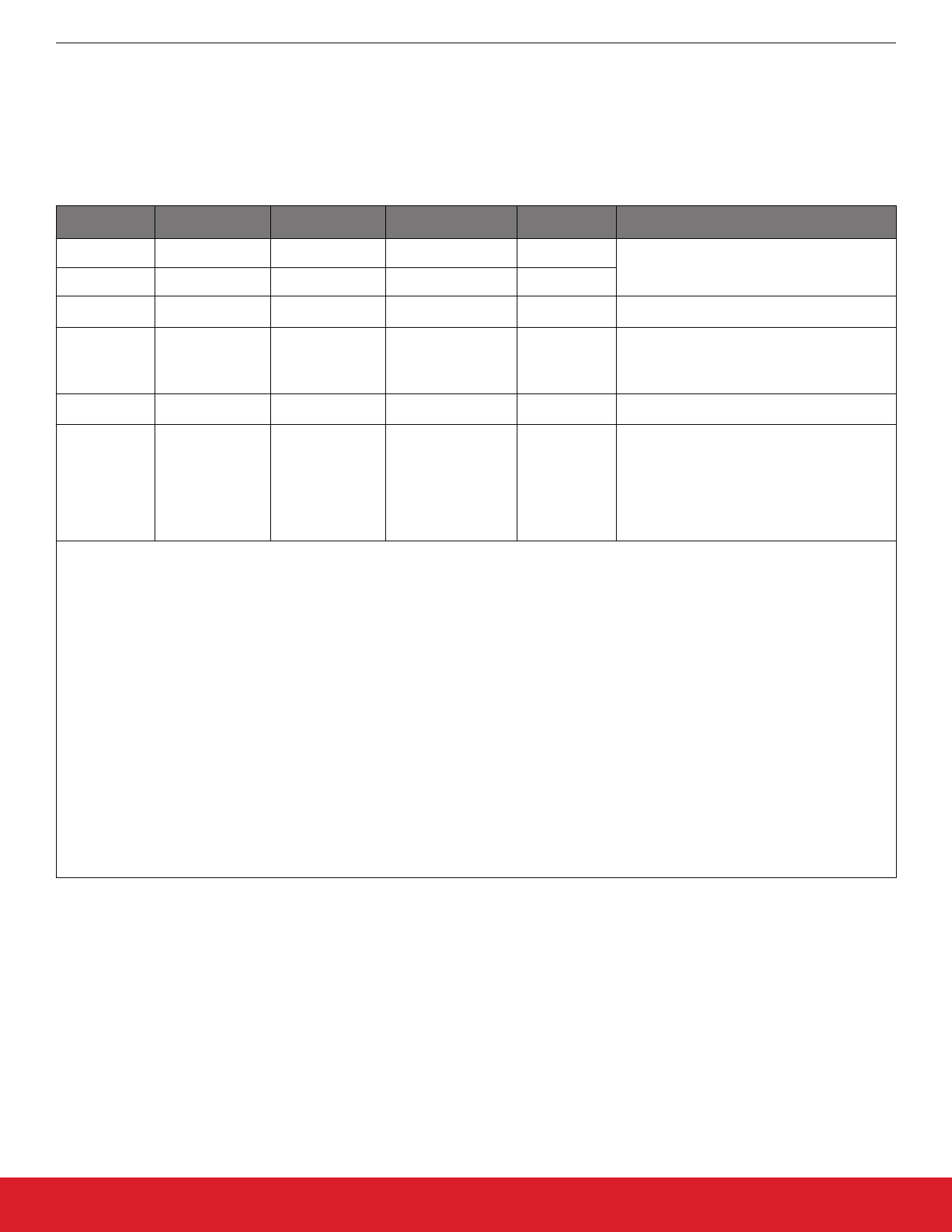

Table 3.1. Si86xx Logic Operation

VI Input1, 2 EN Input1, 2, 3, 4 VDDI State1, 5, 6 VDDO State1, 5, 6 VO Output1, 2

Comments

H H or NC

P

P H Enabled, normal operation.

L H or NC

P

PL

X7 L

P

P

Hi-Z8

Disabled.

X7 H or NC

UP

P L9 Upon transition of VDDI from unpowered to

powered, VO returns to the same state as

H9 VI in less than 1 µs.

X7 L

UP

P

Hi-Z8

Disabled.

X7 X7

P

UP Undetermined Upon transition of VDDO from unpowered

to powered, VO returns to the same state

as VI within 1 µs, if EN is in either the H or

NC state. Upon transition of VDDO from

unpowered to powered, VO returns to Hi-Z

within 1 µs if EN is L.

Note:

1. VDDI and VDDO are the input and output power supplies. VI and VO are the respective input and output terminals. EN is the

enable control input located on the same output side.

2. X = not applicable; H = Logic High; L = Logic Low; Hi-Z = High Impedance.

3. It is recommended that the enable inputs be connected to an external logic high or low level when the Si86xx is operating in noisy

environments.

4. No Connect (NC) replaces EN1 on Si8630/35. No Connect replaces EN2 on the Si8635. No Connects are not internally connec-

ted and can be left floating, tied to VDD, or tied to GND.

5. “Powered” state (P) is defined as 2.5 V < VDD < 5.5 V.

6. “Unpowered” state (UP) is defined as VDD = 0 V.

7. Note that an I/O can power the die for a given side through an internal diode if its source has adequate current.

8. When using the enable pin (EN) function, the output pin state is driven into a high-impedance state when the EN pin is disabled

(EN = 0).

9. See Ordering Guide for details. This is the selectable fail-safe operating mode (ordering option). Some devices have default out-

put state = H, and some have default output state = L, depending on the ordering part number (OPN). For default high devices,

the data channels have pull-ups on inputs/outputs. For default low devices, the data channels have pull-downs on inputs/outputs.

silabs.com | Smart. Connected. Energy-friendly.

Rev. 1.6 | 4

5 Page

Si8630/31/35 Data Sheet

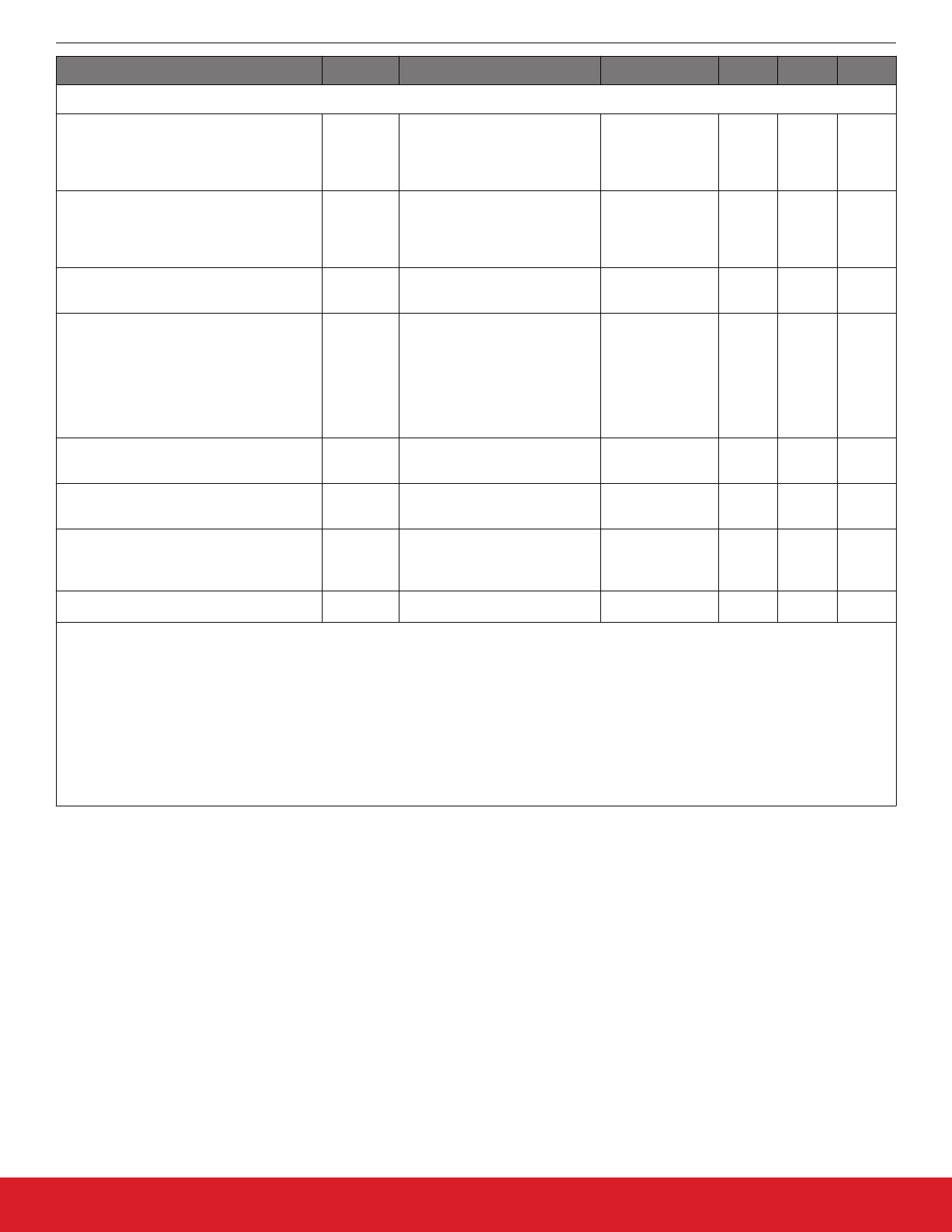

Electrical Specifications

Parameter

Symbol

Test Condition

Min Typ Max Unit

All Models

Output Rise Time

CL = 15 pF

tr See Figure 4.2 Propagation

Delay Timing on page 11

—

2.5 4.0 ns

Output Fall Time

CL = 15 pF

tf See Figure 4.2 Propagation

Delay Timing on page 11

—

2.5 4.0 ns

Peak Eye Diagram Jitter

tJIT(PK)

See Figure 2.3 Eye Diagram

on page 3

—

350 —

ps

VI = VDD or 0 V

Common Mode Transient Immunity

Si86xxxB/C/D

Si86xxxT

CMTI

VCM = 1500 V

See Figure 4.3 Common-

Mode Transient Immunity Test

Circuit on page 11

35

60

kV/µs

50 —

100 —

Enable to Data Valid

ten1 See Figure 4.1 ENABLE Tim-

ing Diagram on page 11

—

6.0 11 ns

Enable to Data Tri-State

ten2 See Figure 4.1 ENABLE Tim-

ing Diagram on page 11

—

8.0 12 ns

Input power loss to valid default output

tSD See Figure 3.1 Device Behav-

ior during Normal Operation

on page 6

—

8.0 12 ns

Start-up Time 4

tSU

— 15 40 µs

Note:

1. VDD1 = 5 V ±10%; VDD2 = 5 V ±10%, TA = –40 to 125 °C

2. The nominal output impedance of an isolator driver channel is approximately 50 Ω, ±40%, which is a combination of the value of

the on-chip series termination resistor and channel resistance of the output driver FET. When driving loads where transmission

line effects will be a factor, output pins should be appropriately terminated with controlled-impedance PCB traces.

3. tPSK(P-P) is the magnitude of the difference in propagation delay times measured between different units operating at the same

supply voltages, load, and ambient temperature.

4. Start-up time is the time period from the application of power to the appearance of valid data at the output.

silabs.com | Smart. Connected. Energy-friendly.

Rev. 1.6 | 10

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet SI8635.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SI8630 | Low-Power Triple-Channel Digital Isolators | Silicon Laboratories |

| SI8631 | Low-Power Triple-Channel Digital Isolators | Silicon Laboratories |

| SI8635 | Low-Power Triple-Channel Digital Isolators | Silicon Laboratories |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |