|

|

PDF ICS8602 Data sheet ( Hoja de datos )

| Número de pieza | ICS8602 | |

| Descripción | DIFFERENTIAL-TO-LVCMOS/LVTTL CLOCK GENERATOR | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS8602 (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

Integrated

Circuit

Systems, Inc.

PRELIMINARY

ICS8602

ZERO DELAY, DIFFERENTIAL-TO-LVCMOS/LVTTL

CLOCK GENERATOR

GENERAL DESCRIPTION

The ICS8602 is a high performance, low skew,

,&6 1-to-9 Differential-to-LVCMOS/LVTTL Zero De-

HiPerClockS™ lay Buffer and a member of the HiPerClockS™

family of High Performance Clocks Solutions

from ICS. The CLK, nCLK pair can accept most

standard differential input levels. The VCO operates at a fre-

quency range of 250MHz to 500MHz. The external feedback

allows the device to achieve “zero delay” between the input

clock and the output clocks. The device is designed only for

1:1 input/output frequency ratios. The output divider allows a

www.DwaitdaeShieneptu4tU/o.cuotmput frequency range with the 250MHz to

500MHz VCO. The PLL_SEL pin can be used to bypass the

PLL for system test and debug purposes. In bypass mode,

the reference clock is routed around the PLL and into the in-

ternal output dividers.The low impedance LVCMOS/LVTTL out-

puts are designed to drive 50Ω series or parallel terminated

transmission lines. The effective fanout can be doubled by

utilizing the ability of the outputs to drive two series termi-

nated lines. The differential reference clock input will accept

any differential signal levels.

FEATURES

• Fully integrated PLL

• 9 LVCMOS/LVTTL outputs, 7Ω typical output impedance

• CLK, nCLK pair can accept the following differential

input levels: LVPECL, LVDS, LVHSTL, SSTL, HCSL

• Output frequency range: 15.625MHz to 250MHz

• Input frequency range: 15.625MHz to 250MHz

• VCO range: 250MHz to 500MHz

• External feedback for “zero delay” clock regeneration

with configurable frequencies

• Cycle-to-cycle jitter: 36ps (typical)

• Output skew: 125ps (maximum)

• Static Phase Offset: TBD±100ps (typical)

• 3.3V supply voltage

• 0°C to 70°C ambient operating temperature

BLOCK DIAGRAM

PIN ASSIGNMENT

SEL0

SEL1

CLK

nCLK

FB_IN

PLL_SEL

MR/nOE

0

÷2

÷4

÷8

PLL 1 ÷16

Q0

Q1 32 31 30 29 28 27 26 25

VDDA 1

Q2

VDD 2

2 4 VDDO

23 Q5

Q3 CLK 3

22 GND

nCLK 4

Q4

GND 5

Q5 DIV_SEL0 6

ICS8602

21 Q4

2 0 VDDO

19 Q3

Q6 DIV_SEL1 7

18 GND

GND 8

17 MR/nOE

Q7

9 10 11 12 13 14 15 16

Q8

32-Lead LQFP

7mm x 7mm x 1.4mm package body

Y Package

Top View

The Preliminary Information presented herein represents a product in prototyping or pre-production. The noted characteristics are based on initial

product characterization. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications without notice.

8602BY

www.icst.com/products/hiperclocks.html

REV. F APRIL 16, 2003

1

1 page

Integrated

Circuit

Systems, Inc.

PRELIMINARY

ICS8602

ZERO DELAY, DIFFERENTIAL-TO-LVCMOS/LVTTL

CLOCK GENERATOR

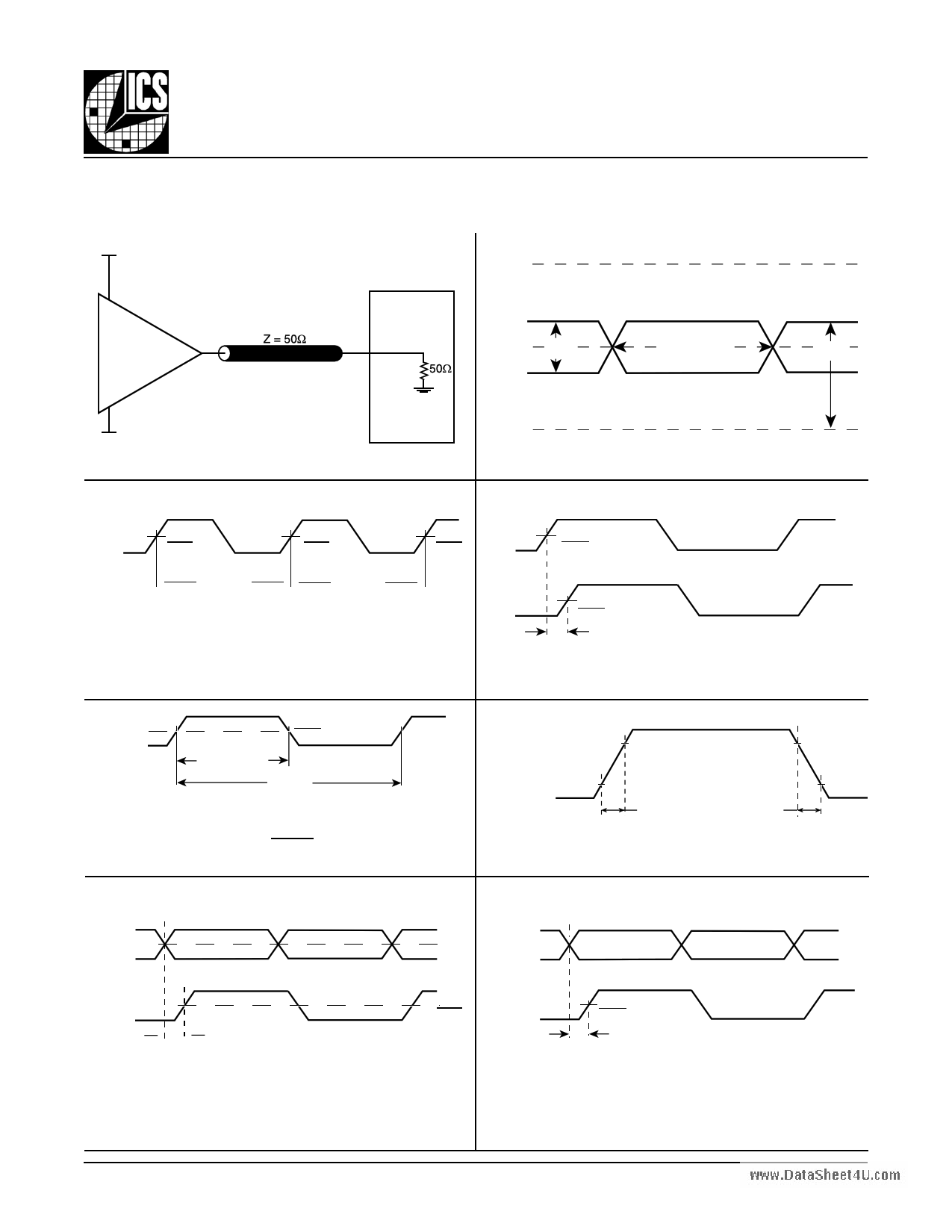

PARAMETER MEASUREMENT INFORMATION

VDD, VDDA, VDDO = 1.65V±5%

LVCMOS

www.DataSheet4U.com

SCOPE

Qx

GND = -1.65V±5%

3.3V OUTPUT LOAD AC TEST CIRCUIT

VDD

nCLK

CLK

V

PP

Cross Points

GND

DIFFERENTIAL INPUT LEVEL

V

CMR

Q0:Q8

V

DDO

2

tcycle n

V

DDO

2

➤ tcycle n+1

t jit(cc) = tcycle n –tcycle n+1

1000 Cycles

V

DDO

2

➤

Qx

Qy

V

DDO

2

V

DDO

2

t sk(o)

CYCLE-TO-CYCLE JITTER

Q0:Q8

V

DDO

2

Pulse Width

t

PERIOD

odc & tPERIOD

odc = t PW

t PERIOD

OUTPUT SKEW

20%

Clock Outputs

80%

t

R

OUTPUT RISE/FALL TIME

80%

t

F

20%

nCLK

CLK

nCLK

CLK

FB_IN

➤ t (Ø)

VDD

2

t(Ø) mean = Static Phase Offset

(where t(Ø) is any random sample, and t(Ø) mean is the average

of the sampled cycles measured on controlled edges)

Q0:Q8

VDDO

2

t

PD

STATIC PHASE OFFSET

8602BY

PROPAGATION DELAY

www.icst.com/products/hiperclocks.html

5

REV. F APRIL 16, 2003

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet ICS8602.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS8602 | DIFFERENTIAL-TO-LVCMOS/LVTTL CLOCK GENERATOR | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |