|

|

PDF XR16M780 Data sheet ( Hoja de datos )

| Número de pieza | XR16M780 | |

| Descripción | 1.62V TO 3.63V HIGH PERFORMANCE UART | |

| Fabricantes | Exar Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XR16M780 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

XR16M780

1.62V TO 3.63V HIGH PERFORMANCE UART WITH 64-BYTE FIFO

SEPTEMBER 2008

REV. 1.0.0

GENERAL DESCRIPTION

The XR16M7801 (M780) is an enhanced Universal

Asynchronous Receiver and Transmitter (UART) with

64 bytes of transmit and receive FIFOs,

programmable transmit and receive FIFO trigger

levels, automatic hardware and software flow control,

and data rates of up to 16 Mbps at 3.3V, 12.5 Mbps at

2.5V and 7.5 Mbps at 1.8V with 4X data sampling

rate.

The Auto RS-485 Half-Duplex Direction control

feature simplifies both the hardware and software for

half-duplex RS-485 applications. In addition, the

Multidrop mode with Auto Address detection

increases the performance by simplifying the

software routines.

The Independent TX/RX Baud Rate Generator

feature allows the transmitter and receiver to operate

at different baud rates. Power consumption of the

M780 can be minimized by enabling the sleep mode

and PowerSave mode.

The M780 has a 16550 compatible register set that

provide users with operating status and control,

receiver error indications, and modem serial interface

controls. An internal loopback capability allows

onboard diagnostics. The M780 is available in 32-pin

QFN, 48-pin TQFP and 25-pin BGA packages. All

three packages offer both the 16 mode (Intel bus)

interface and the 68 mode (Motorola bus) interface

which allows easy integration with Motorola

processors.

www.DataShNeOeTt4EU: .c1oCmovered by U.S. Patent #5,649,122.

FEATURES

• Pin-to-pin compatible with XR16L580 in 32-QFN

and 48-TQFP packages

• Intel or Motorola Bus Interface select

• 16Mbps maximum data rate

• Programmable TX/RX FIFO Trigger Levels

• TX/RX FIFO Level Counters

• Independent TX/RX Baud Rate Generator

• Fractional Baud Rate Generator

• Auto RTS/CTS Hardware Flow Control

• Auto XON/XOFF Software Flow Control

• Auto RS-485 Half-Duplex Direction Control

• Multidrop mode w/ Auto Address Detect

• Sleep Mode with Automatic Wake-up

• PowerSave mode

• Infrared (IrDA 1.0 and 1.1) mode

• 1.62V to 3.63V supply operation

• Crystal oscillator or external clock input

APPLICATIONS

• Personal Digital Assistants (PDA)

• Cellular Phones/Data Devices

• Battery-Operated Devices

• Global Positioning System (GPS)

• Bluetooth

FIGURE 1. XR16M780 BLOCK DIAGRAM

PwrSave

A2:A0

D 7 :D 0

IO R #

IOW# (R/W#)

CS#

INT (IRQ#)

RESET

(RESET#)

16/68#

Intel or

M o to ro la

Data Bus

Interface

UART

UART 64 Byte TX FIFO

Regs TX &

RX

IR

ENDEC

BRG 64 Byte RX FIFO

Crystal Osc/Buffer

VCC

(1.62 to 3.63 V)

GND

TX, RX,

RTS#, CTS#,

DTR#, DSR#,

RI#, CD#

XTAL1

XTAL2

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

1 page

REV. 1.0.0

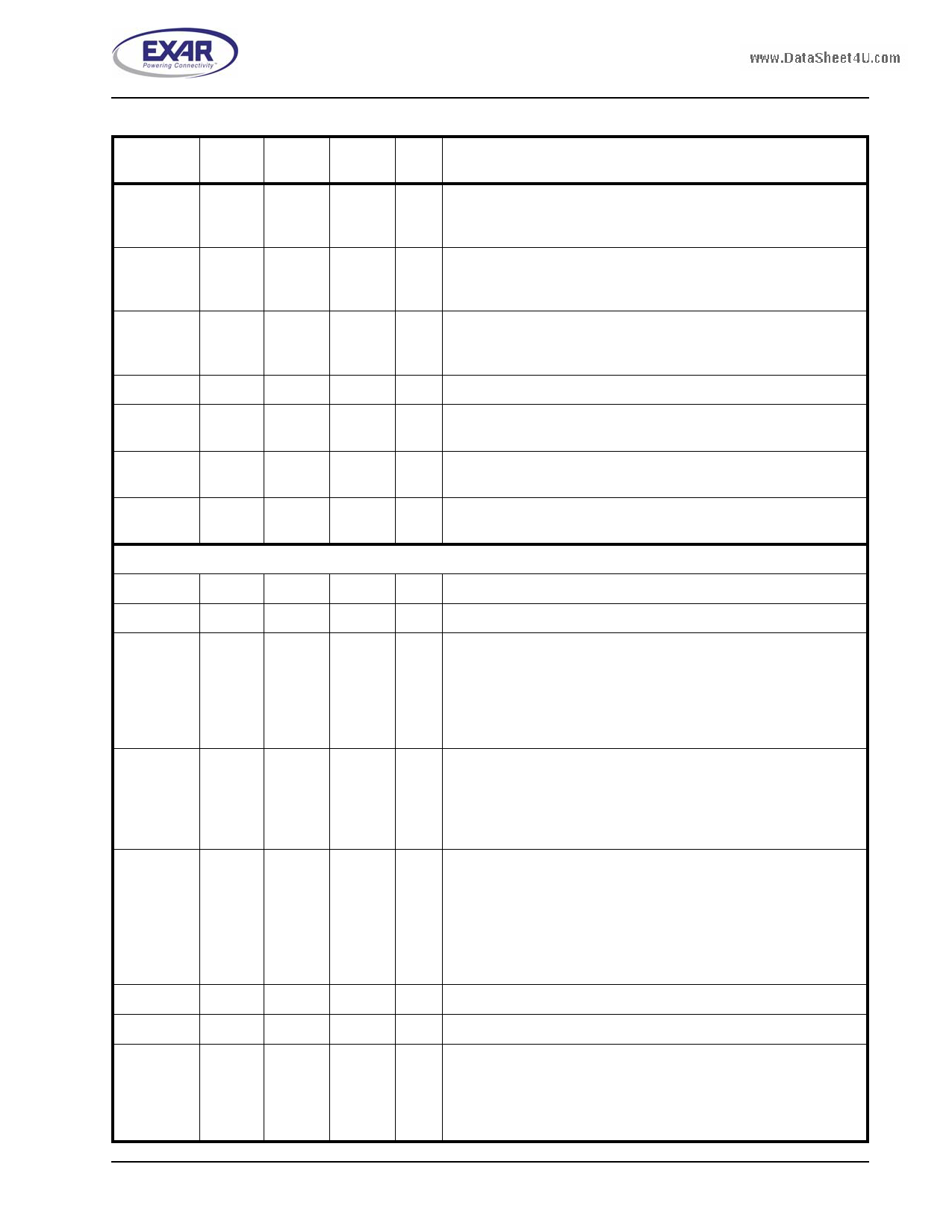

Pin Description

XR16M780

1.62V TO 3.63V HIGH PERFORMANCE UART WITH 64-BYTE FIFO

NAME

RX

RTS#

CTS#

DTR#

DSR#

CD#

RI#

32-QFN 48-TQFP 25-BGA

PIN#

PIN#

PIN#

TYPE

DESCRIPTION

6 7 E4 I UART Receive Data or infrared receive data. Normal receive data

input must idle at logic 1 condition. The infrared receiver idles at

logic 0. This input should be connected to VCC when not used.

21 32 B3 O UART Request-to-Send (active low) or general purpose output.

This output must be asserted prior to using auto RTS flow control,

see EFR[6], MCR[1] and IER[6].

24 38 A1 I UART Clear-to-Send (active low) or general purpose input. It can

be used for auto CTS flow control, see EFR[7], MSR[4] and IER[7].

This input should be connected to VCC when not used.

22 33

- O UART Data-Terminal-Ready (active low) or general purpose output.

25 39

- I UART Data-Set-Ready (active low) or general purpose input. This

input should be connected to VCC when not used.

26 40

- I UART Carrier-Detect (active low) or general purpose input. This

input should be connected to VCC when not used.

27 41

- I UART Ring-Indicator (active low) or general purpose input. This

input should be connected to VCC when not used.

ANCILLARY SIGNALS

XTAL1

10

XTAL2

11

PwrSave

9

14

15

13

www.DataSheet4U.com

16/68#

2

1

RESET

(RESET#)

23

35

VCC

GND

GND

28

13

Center

Pad

42

18

-

D5 I Crystal or external clock input.

- O Crystal or buffered clock output.

C4 I Power-Save (active high). This feature isolates the M780’s data bus

interface from the host preventing other bus activities that cause

higher power drain during sleep mode. See Sleep Mode with Auto

Wake-up and Power-Save Feature section for details. This pin does

not have an internal pull-down resistor. This input should be con-

nected to GND when not used.

B2 I Intel or Motorola Bus Select. When 16/68# pin is at logic 1, 16 or

Intel Mode, the device will operate in the Intel bus type of interface.

When 16/68# pin is at logic 0, 68 or Motorola mode, the device will

operate in the Motorola bus type of interface. This pin does not

have an internal pull-up or pull-down resistor.

A2 I When 16/68# pin is at logic 1 for Intel bus interface, this input

becomes RESET (active high). When 16/68# pin is at logic 0 for

Motorola bus interface, this input becomes RESET# (active low).

A 40 ns minimum active pulse on this pin will reset the internal reg-

isters and all outputs of the UART. The UART transmitter output will

be held at logic 1, the receiver input will be ignored and outputs are

reset during reset period (see UART Reset Conditions).

B1 Pwr 1.62V to 3.63V power supply.

E5 Pwr Power supply common, ground.

- Pwr The center pad on the backside of the QFN package is metallic and

should be connected to GND on the PCB. The thermal pad size on

the PCB should be the approximate size of this center pad and

should be solder mask defined. The solder mask opening should be

at least 0.0025" inwards from the edge of the PCB thermal pad.

5

5 Page

XR16M780

REV. 1.0.0

1.62V TO 3.63V HIGH PERFORMANCE UART WITH 64-BYTE FIFO

2.3 Device Reset

The RESET input resets the internal registers and the serial interface outputs to their default state (see

Table 18). An active high pulse of longer than 40 ns duration will be required to activate the reset function in

the device. Following a power-on reset or an external reset, the M780 is software compatible with previous

generation of UARTs, XR16L580 and ST16C550.

2.4 Internal Registers

The M780 has a set of 16550 compatible registers for controlling, monitoring and data loading and unloading.

These registers function as data holding registers (THR/RHR), interrupt status and control registers (ISR/IER),

a FIFO control register (FCR), receive line status and control registers (LSR/LCR), modem status and control

registers (MSR/MCR), programmable data rate (clock) divisor registers (DLL/DLM/DLD), and a user accessible

scratchpad register (SPR).

Beyond the general 16C550 features and capabilities, the M780 offers enhanced feature registers (EFR, Xon1/

Xoff 1, Xon2/Xoff 2, DLD, FCTR, EMSR, FC and TRIG) that provide automatic RTS and CTS hardware flow

control, automatic Xon/Xoff software flow control, 9-bit (Multidrop) mode, auto RS-485 half duplex control,

different baud rate for TX and RX and fractional baud rate generator. All the register functions are discussed in

full detail later in “Section 3.0, UART INTERNAL REGISTERS” on page 25.

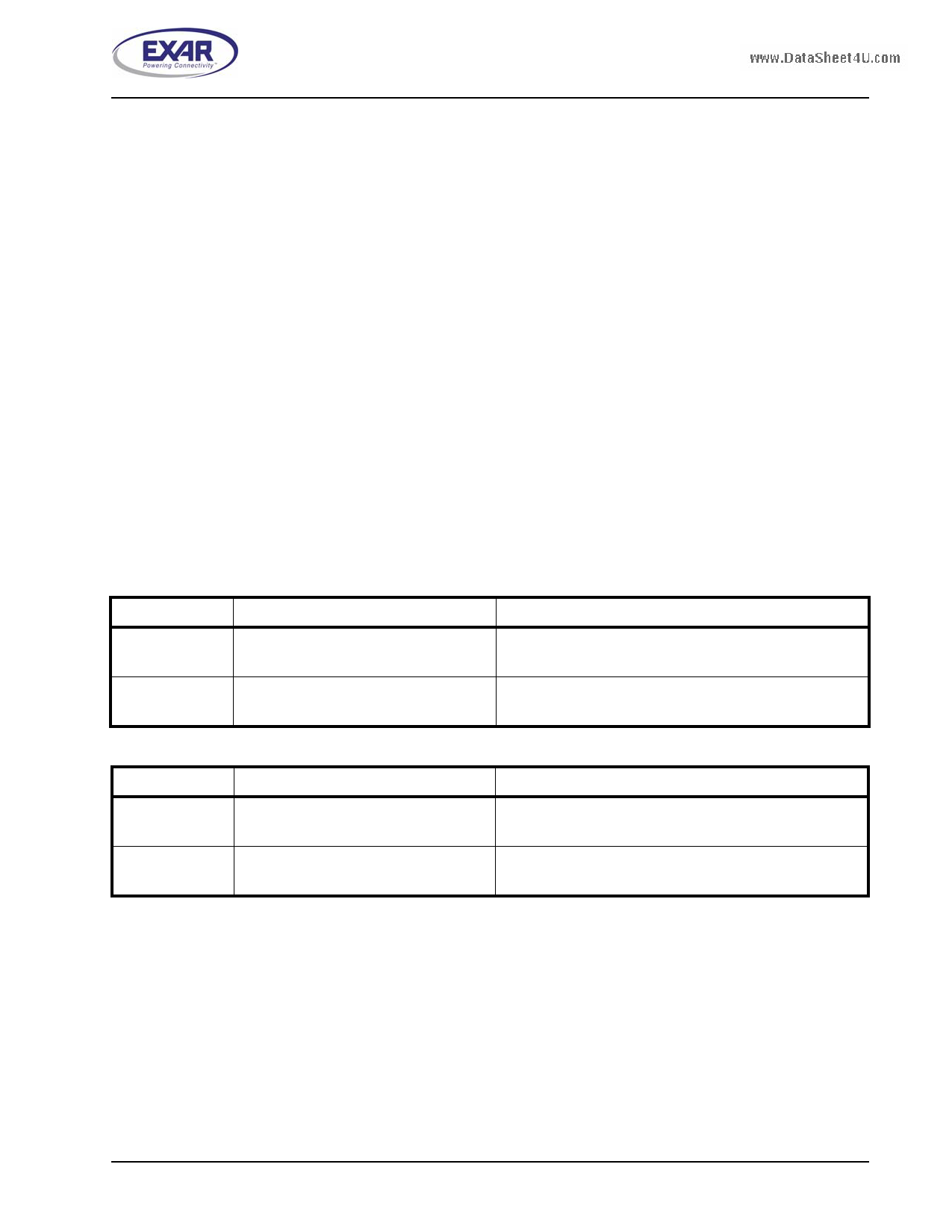

2.5 INT Ouput

The interrupt outputs change according to the operating mode and enhanced features setup. Table 1 and 2

summarize the operating behavior for the transmitter and receiver. Also see Figure 22 through 25.

NOTE: The IRQ# pin requires a pull-up resistor for proper operation.

INT Pin

(16/68# = 1)

IRQ# Pin

(16/68# = 0)

TABLE 1: INT PIN OPERATION FOR TRANSMITTER

FCR BIT-0 = 0 (FIFO DISABLED)

FCR BIT-0 = 1 (FIFO ENABLED)

LOW = One byte in THR

HIGH = THR empty

LOW = FIFO above trigger level

HIGH = FIFO below trigger level or FIFO empty

HIGH = One byte in THR

LOW = THR empty

HIGH = FIFO above trigger level

LOW = FIFO below trigger level or FIFO empty

www.DataSheet4U.com

INT Pin

(16/68# = 1)

IRQ# Pin

(16/68# = 0)

TABLE 2: INT PIN OPERATION FOR RECEIVER

FCR BIT-0 = 0 (FIFO DISABLED)

HIGH = One byte in RHR

LOW = RHR empty

FCR BIT-0 = 1 (FIFO ENABLED)

LOW = FIFO below trigger level

HIGH = FIFO above trigger level or RX Data Timeout

LOW = One byte in RHR

HIGH = RHR empty

HIGH = FIFO below trigger level

LOW = FIFO above trigger level or RX Data Timeout

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet XR16M780.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XR16M780 | 1.62V TO 3.63V HIGH PERFORMANCE UART | Exar Corporation |

| XR16M781 | 1.62V TO 3.63V UART | Exar Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |