|

|

PDF AT572D940HF Data sheet ( Hoja de datos )

| Número de pieza | AT572D940HF | |

| Descripción | DIOPSIS 940HF ARM926EJ-S PLUS ONE GFLOPS DSP | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT572D940HF (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

Features

• DIOwPwSwI.SD®atDaSuhaeleCt4oUr.ecoSmystem Integrating an ARM926EJ-S™ ARM® Thumb® Processor

Core and a MagicV of VLIW Magic DSP™ is optimized for Audio, Communication and

Beam-forming Applications

• High Performance MagicV VLIW DSP

– 1 GFLOPS - 1.6 Gops at 100 MHz

– AHB Master Port, integrated DMA Engine and AHB Slave Port

– Up to 10 Arithmetic Operations per Cycle (4 Multiply, 2 Add/Subtract, 1 Add, 1

Subtract 40-bit Floating Point and 32-bit Integer) allowing Single Cycle FFT

Butterfly

– Native Support for Complex Arithmetic and Vectorial SIMD Operations: One

Complex Multiply with Dual Add/Sub per Clock Cycle or Two Multiply and Two

Add/sub or Simple Scalar Operations

– 32-bit Integer and IEEE® 40-bit Extended Precision Floating Point Numeric Format

– 16-port Data Register File: 256 Registers organized in Two 128-register Banks

– 5-issue predicated VLIW Architecture with Orthogonal ISA, Code Compression

and Hardware Support for Code Efficient Software Pipeline Loops

– 6 Accesses per Cycle Data Memory System (4 Accesses per Cycle for VLIW

Operations + 2 Accesses per Cycle for DMA Transfers) supported by Flexible

Addressing Capability

– 2 Independent Address Generation Units Operating on a 64-register Address

Register File Supporting Complex or Micro-Vectorial Accesses and DSP features:

Programmable Stride and Circular Buffers

– 1.7 Mbits of On-chip SRAM:

– 16 K x 40-bit Data Memory Locations (6 Memory Accesses per Cycle)

– 8 K x 128-bit Dual Port Program Memory Location, Equivalent to ~50K DSP

Assembler Instructions (typical) thanks to Code Compression and SW Pipelining

– DMA Access to the External Program and Data Memory

– Three Main Operating Modes: Run, Debug and Sleep

– User Mode and Privileged Interrupt Service Mode

– Efficient Optimizing Assembler and C-Oriented Architecture: allows Easy

Exploitation of the available Hardware Parallelism

– ARM926EJ-S ARM Thumb Processor

– DSP Instruction Extensions

– ARM Jazelle® Technology for Java® Acceleration

– 16-KByte Data Cache, 16-KByte Instruction Cache, Write Buffer

– 220MIPS at 200MHz

– Memory Management Unit

– EmbeddedICE™ In-circuit Emulation, Debug Communication Channel Support

• Additional Embedded Memories

– 32-KByte of internal ROM, two-cycle access at maximum bus speed

– 48-KByte of internal SRAM, single-cycle access at maximum processor or bus

speed

• External Bus Interface (EBI)

– Supports SDRAM, Static Memory, SmartMedia™ and NAND Flash, CompactFlash™

• USB

– USB 2.0 Full Speed (12 Mbits per second) Host Double Port

– Dual On-chip Transceivers

– Integrated FIFOs and Dedicated DMA Channels

DIOPSIS 940HF

ARM926EJ-S PLUS

ONE GFLOPS DSP

AT572D940HF

Preliminary

7010A–DSP–07/08

1 page

AT572D940HF Preliminary

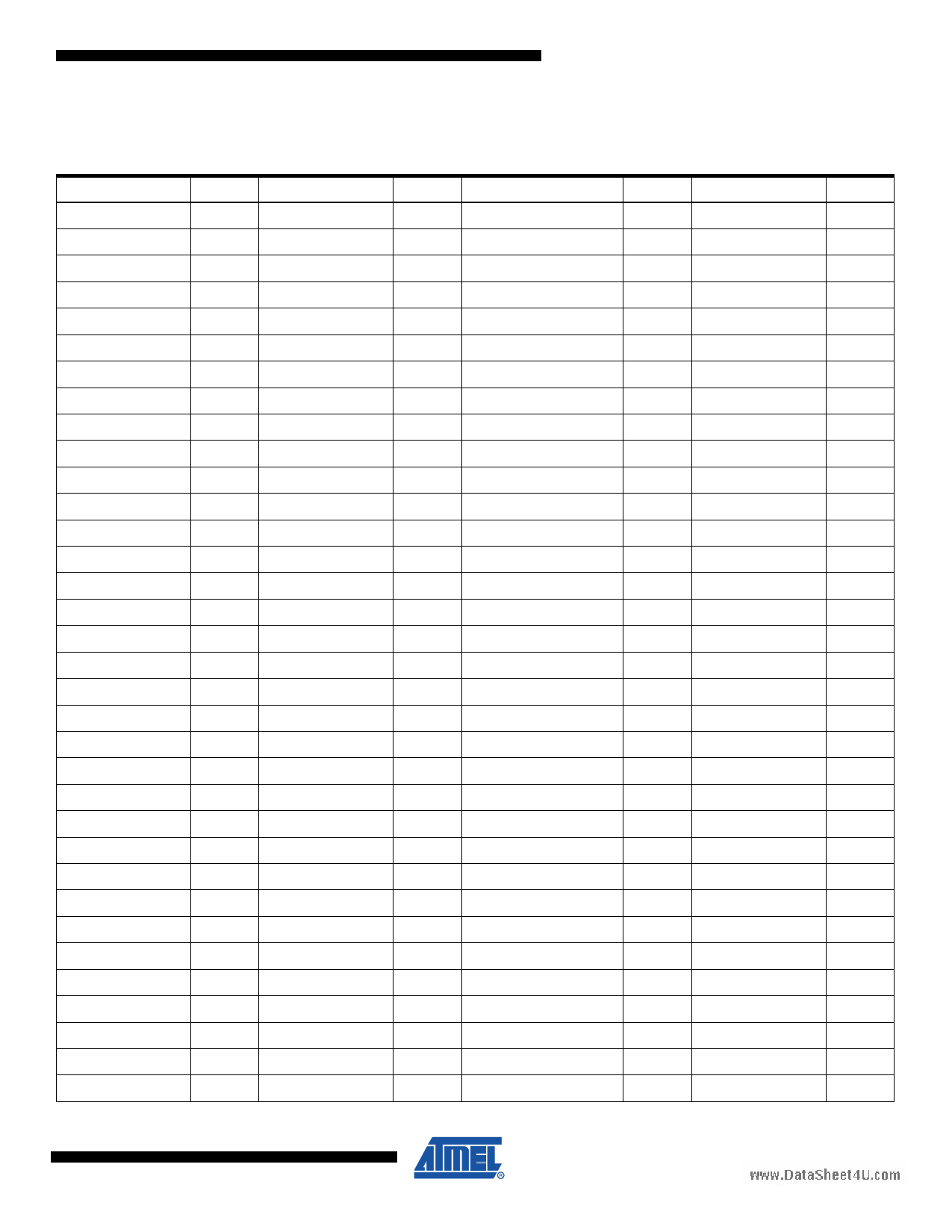

2. Ball Configuration

www.DataSheet4U.com

Table 2-1. AT572D940HF Ball Assignment (I/O: 191 balls)

Name

Pin Name

Pin Name

A0/NBS0

B2 D5

K7 NCS2

A1/NBS2/NWR2 C2

D6

K5 NCS3/SM_NCS

A2 C1 D7 K1 NRD/NOE/CF_NOE

A3 D4 D8 K2 NRST

A4 D3 D9 K6 NWR0/NWE/CF_NWE

A5

D1 D10

K8 NWR1/NBS1/CF_NIOR

A6

E4 D11

L5 NWR3/NBS3/CF_NIOW

A7

E3 D12

L1 PIOA0

A8

F6 D13

L2 PIOA1

A9

G6 D14

L4 PIOA2

A10 F3 D15 L7 PIOA3

A11 H8 D16 M3 PIOA4

A12 F2 D17 L8 PIOA5

A13 F1 D18 M4 PIOA6

A14 G3 D19 M5 PIOA7

A15 H7 D20 M6 PIOA8

A16/SD_BA0 G1 D21

N1 PIOA9

A17/SD_BA1 G2 D22

M7 PIOA10

A18 H6 D23 N4 PIOA11

A19 H3 D24 N5 PIOA12

A20 J8 D25 P1 PIOA13

A21 H2 D26 P3 PIOA14

A_JCFG

N16 D27

P4 PIOA15

A_RTCK

M17 D28

P5 PIOA16

A_TCK

N17 D29

R1 PIOA17

A_TDI

M14 D30

R2 PIOA18

A_TDO

M16 D31

R3 PIOA19

A_TMS

N15 M_NTRST

E16 PIOA20

A_NTRST

M13 M_TCK

F13 PIOA21

D0

H1 M_TDI

E15 PIOA22

D1

J7 M_TDO

E14 PIOA23

D2

J2 M_TMS

E17 PIOA24

D3

J1 NCS0

F7 PIOA25

D4

K9

NCS1/SD_CS

A6

PIOA26

Pin

B7

E7

B6

J17

C6

D6

G7

F11

C11

A11

B11

H10

G10

D10

B17

A17

B16

A16

C15

H17

V15

U15

V16

T15

V17

T16

T17

U18

T18

R15

R18

H16

B9

D9

Name

PIOA27

PIOA28

PIOA29

PIOA30

PIOA31

PIOB0

PIOB1

PIOB2

PIOB3

PIOB4

PIOB5

PIOB6

PIOB7

PIOB8

PIOB9

PIOB10

PIOB11

PIOB12

PIOB13

PIOB14

PIOB15

PIOB16

PIOB17

PIOB18

PIOB19

PIOB20

PIOB21

PIOB22

PIOB23

PIOB24

PIOB25

PIOB26

PIOB27

PIOB28

Pin

G9

J9

A8

D8

B8

U8

L9

P9

R9

V9

L10

N10

V10

T10

P10

M10

N11

M11

L11

U12

T12

R12

N12

V13

U13

T13

P13

V14

R14

J10

H15

B12

A12

F9

7010A–DSP–07/08

5

5 Page

AT572D940HF Preliminary

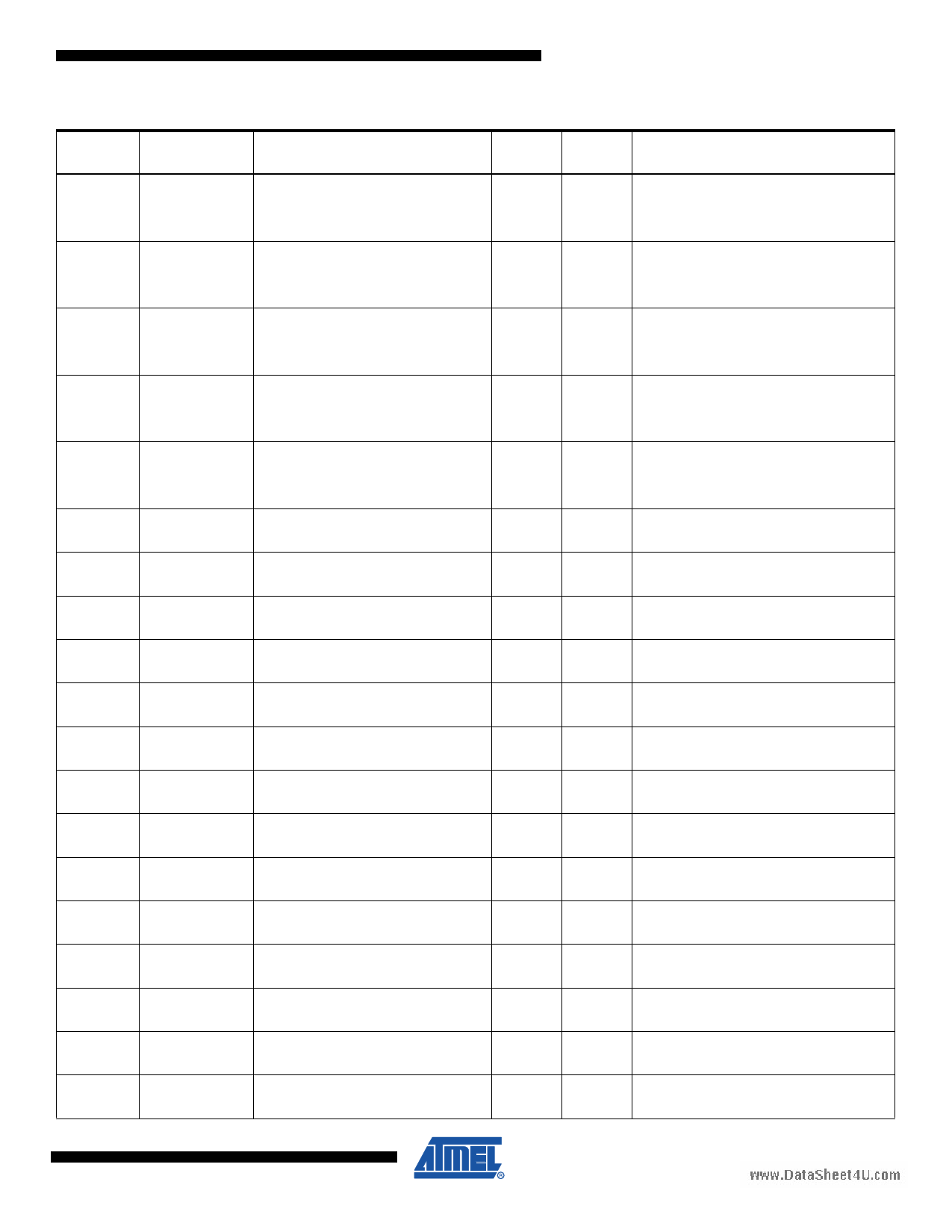

Table 3-1. AT572D940HF Pin Description (Continued)

www.DataSheet4U.com

Module Name

Function

SPI

SPI1_MOSI

SPI 1 Master Out/Slave In data

SPI

SPI1_MISO

SPI 1 Master In/Slave Out data

SPI

SPI

SPI

SSC

SSC

SSC

SSC

SSC

SSC

SSC

SSC

SSC

SSC

SSC

SSC

SSC

SSC

SPI1_NCS0

SPI 1 Input/Output Chip select

SPI1_NCS1 -

SPI1_NCS3

SPI 1 Output Chip Selects

SPI1_CK

SSC0_TXD

SSC0_RXD

SSC0_TF

SSC0_RF

SSC0_TK

SSC0_RK

SSC1_TXD

SSC1_RXD

SSC1_TF

SSC1_RF

SSC1_TK

SSC1_RK

SSC2_TXD

SSC2_TF

SPI 1 Serial clock

Synchronous Serial Controller 0

Data Out

Synchronous Serial Controller 0

Data In

Synchronous Serial Controller 0

Transmit Frame Clock

Synchronous Serial Controller 0

Receive Frame Clock

Synchronous Serial Controller 0

Transmit Bit Clock

Synchronous Serial Controller 0

Receive Bit Clock

Synchronous Serial Controller 1

Data Out

Synchronous Serial Controller 1

Data In

Synchronous Serial Controller 1

Transmit Frame Clock

Synchronous Serial Controller 1

Receive Frame Clock

Synchronous Serial Controller 1

Transmit Bit Clock

Synchronous Serial Controller 1

Receive Bit Clock

Synchronous Serial Controller 2

Data Out

Synchronous Serial Controller 2

Transmit Frame Clock

Type

bi-03

bi-03

out-03

bi-03

bi-03

bi-03

Active

Level

low

low

Notes

through PIO line

SPI SLV ! data input

SPI MST ! data output

through PIO line

SPI SLV ! data output

SPI MST ! data input

through PIO line

SPI SLV ! CS Input

SPI MST ! CS 0 Output

output through PIO line

SPI SLV ! n.a.

SPI MST ! CS 3, 2, 1 Outputs

through PIO line

SPI SLV ! clock input

SPI MST ! clock output

output through PIO line

bi-03

input through PIO line

bi-03

through PIO line

bi-03

through PIO line

bi-03

through PIO line

bi-03

through PIO line

bi-03

output through PIO line

bi-03

input through PIO line

bi-03

through PIO line

bi-03

through PIO line

bi-03

through PIO line

bi-03

through PIO line

bi-03

output through PIO line

bi-03

through PIO line

7010A–DSP–07/08

11

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet AT572D940HF.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT572D940HF | DIOPSIS 940HF ARM926EJ-S PLUS ONE GFLOPS DSP | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |