|

|

PDF SY100S351 Data sheet ( Hoja de datos )

| Número de pieza | SY100S351 | |

| Descripción | Hex D Flip-flop | |

| Fabricantes | Micrel Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SY100S351 (archivo pdf) en la parte inferior de esta página. Total 7 Páginas | ||

|

No Preview Available !

HEX D FLIP-FLOP

SY100S351

FINAL

FEATURES

DESCRIPTION

s Max. toggle frequency of 700MHz

s Clock to Q max. of 1200ps

s IEE min. of –98mA

s Industry standard 100K ECL levels

s Extended supply voltage option:

VEE = –4.2V to –5.5V

s Voltage and temperature compensation for improved

noise immunity

s Internal 75KΩ input pull-down resistors

The SY100S351 offers six D-type, edge-triggered,

master/slave flip-flops with differential outputs, and is

designed for use in high-performance ECL systems. The

flip-flops are controlled by the signal from the logical OR

operation on a pair of common clock signals (CPa, CPb).

Data enters the master when both CPa and CPb are LOW

and transfers to the slave when either CPa or CPb (or both)

go to a logic HIGH. The Master Reset (MR) input overrides

all other inputs and takes the Q outputs to a logic LOW. The

inputs on this device have 75KΩ pull-down resistors.

s 50% faster than Fairchild 300K

s Better than 20% lower power than Fairchild

PIN CONFIGURATIONS

s Function and pinout compatible with Fairchild F100K

s Available in 24-pin CERPACK and 28-pin PLCC

packages

11 10 9 8 7 6 5

BLOCK DIAGRAM

D2

D3

VEE

VEES

MR

www.DataSheet4U.coCmPa

CPb

12

13

14

15

16

17

18

Top View

PLCC

J28-1

4 Q2

3 Q2

2 VCCA

1 VCC

28 VCC

27 Q3

26 Q3

19 20 21 22 23 24 25

D5

DQ

Q5

CPb

CPa

ER Q

Q5

MR

D4

DQ

Q4

ER Q

Q4

D3

DQ

Q3

ER Q

Q3

24 23 22 21 20 19

D4 1

18 D1

D5 2

17 D0

Q5 3

Q5 4

Q4 5

Top View

Flatpack

F24-1

16

15

14

Q0

Q0

Q1

Q4 6

13 Q1

7 8 9 10 11 12

D2

DQ

Q2

ER Q

Q2

D1

DQ

Q1

ER Q

Q1

D0

DQ

Q0

ER Q

Q0

Rev.: G Amendment: /0

1 Issue Date: July, 1999

1 page

Micrel

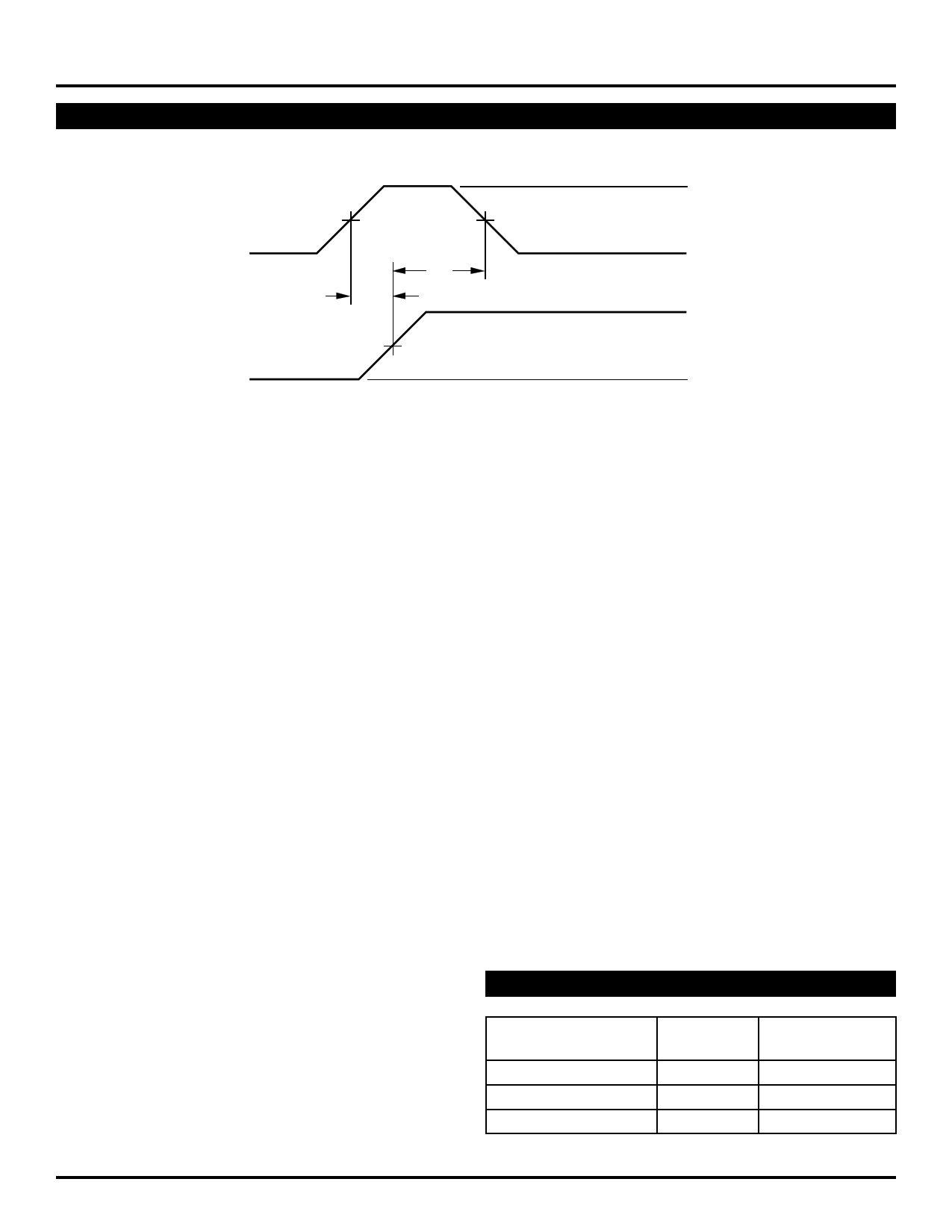

TIMING DIAGRAMS

DATA

CLOCK

tS

50%

tH

50%

Data Set-up and Hold Time

NOTES:

1. VEE = –4.2V to –5.5V unless otherwise specified; VCC = VCCA = GND

2. tS is the minimum time before the transition of the clock that information

must be present at the data input.

3. tH is the minimum time after the transition of the clock that information must

remain unchanged at the data input.

SY100S351

–0.95V

–1.69V

–0.95V

–1.69V

PRODUCT ORDERING CODE

Ordering

Code

SY100S351FC

SY100S351JC

SY100S351JCTR

Package

Type

F24-1

J28-1

J28-1

Operating

Range

Commercial

Commercial

Commercial

5

5 Page | ||

| Páginas | Total 7 Páginas | |

| PDF Descargar | [ Datasheet SY100S351.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SY100S350 | Hex D-latch | Micrel Semiconductor |

| SY100S351 | Hex D Flip-flop | Micrel Semiconductor |

| SY100S355 | Quad Multiplexer/latch | Micrel Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |