|

|

PDF HY5V52F Data sheet ( Hoja de datos )

| Número de pieza | HY5V52F | |

| Descripción | 4Banks x 2M x 32bits Synchronous DRAM | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HY5V52F (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Preliminary

HY5V52(L)F(P) Series

4Banks x 2M x 32bits Synchronous DRAM

Document Title

4Bank x 2M x 32bits Synchronous DRAM

Revision History

Revision No.

0.1

History

Initial Draft

Draft Date

Jun. 2004

Remark

Preliminary

This document is a general product description and is subject to change without notice. Hynix does not assume any responsibility for

use of circuits described. No patent licenses are implied.

Rev. 0.1 / June. 2004

1

1 page

Preliminary

HY5V52(L)F(P) Series

4Banks x 2M x 32bits Synchronous DRAM

FUNCTIONAL BLOCK DIAGRAM

2Mbit x 4banks x 32 I/O Synchronous DRAM

CLK

CKE

CS

RAS

CAS

WE

DQM0

DQM1

DQM2

DQM3

Self refresh

logic & timer

Row Active

Internal Row

Counter

Row

Pre

Decoder

Refresh

Column Active

Column

Pre

Decoder

2Mx32 BANK 3

2Mx32 BANK 2

2Mx32 BANK 1

2Mx32 BANK 0

Memory

Cell

Array

Y-Decoder

DQ0

DQ31

Bank Select

Column Add

Counter

A0 Address

A1

Register

Burst

Counter

Pipe Line

A11

BA1

Mode Register

CAS Latency

Data Out Control

Control

BA0

Rev. 0.1 / June. 2004

5

5 Page

Preliminary

HY5V52(L)F(P) Series

4Banks x 2M x 32bits Synchronous DRAM

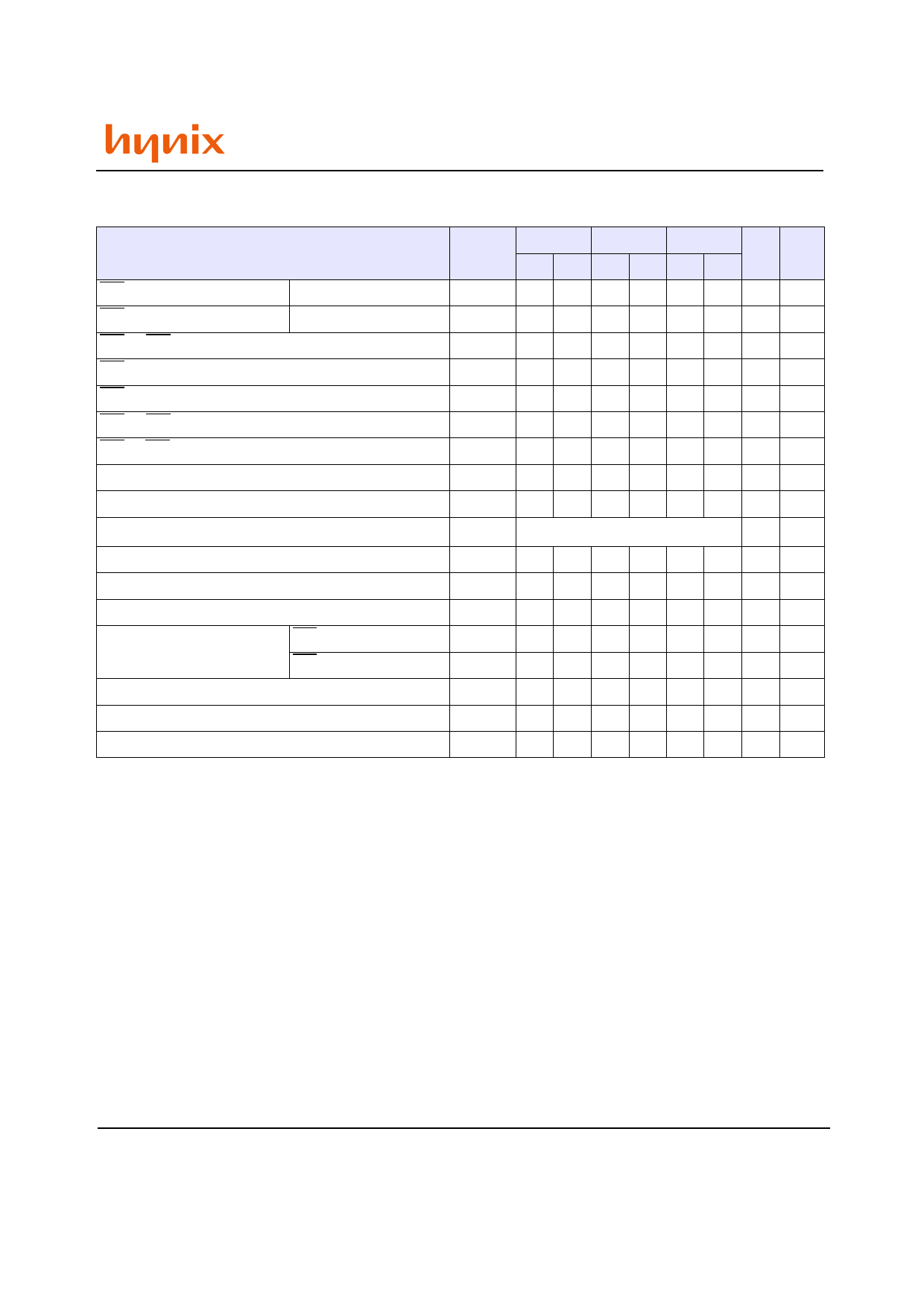

AC CHARACTERISTICS II (AC operating conditions unless otherwise noted)

Parameter

RAS Cycle Time

Operation

RAS Cycle Time

Auto Refresh

RAS to CAS Delay

RAS Active Time

RAS Precharge Time

RAS to RAS Bank Active Delay

CAS to CAS Delay

Write Command to Data-In Delay

Data-in to Precharge Command

Data-In to Active Command

DQM to Data-Out Hi-Z

DQM to Data-In Mask

MRS to New Command

Precharge to Data Output

High-Z

CAS Latency=3

CAS Latency=2

Power Down Exit Time

Self Refresh Exit Time

Refresh Time

HPS

Symbol

Unit Note

Min Max Min Max Min Max

tRC 65 - 70 - 70 - ns

tRRC

65 - 70 - 70 - ns

tRCD

20 - 20 - 20 - ns

tRAS 45 100K 50 100K 50 100K ns

tRP 20 - 20 - 20 - ns

tRRD

15 - 20 - 20 - ns

tCCD

1 - 1 - 1 - CLK

tWTL

0 - 0 - 0 - CLK

tDPL 2 - 2 - 2 - CLK

tDAL

tDQZ

tDPL + tRP

2 - 2 - 2 - CLK

tDQM

0 - 0 - 0 - CLK

tMRD

2 - 2 - 2 - CLK

tPROZ3

3 - 3 - 3 - CLK

tPROZ2

2 - 2 - 2 - CLK

tDPE

1 - 1 - 1 - CLK

tSRE 1 - 1 - 1 - CLK 1

tREF - 64 - 64 - 64 ms

Note :

1. A new command can be given tRC after self refresh exit.

Rev. 0.1 / June. 2004

11

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet HY5V52F.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HY5V52F | 4Banks x 2M x 32bits Synchronous DRAM | Hynix Semiconductor |

| HY5V52FP | 4Banks x 2M x 32bits Synchronous DRAM | Hynix Semiconductor |

| HY5V52LF | 4Banks x 2M x 32bits Synchronous DRAM | Hynix Semiconductor |

| HY5V52LFP | 4Banks x 2M x 32bits Synchronous DRAM | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |