|

|

PDF ICS1889 Data sheet ( Hoja de datos )

| Número de pieza | ICS1889 | |

| Descripción | 100Base-FX Integrated PHYceiverTM | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS1889 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Integrated

Circuit

Systems, Inc.

ICS1889

100Base-FX Integrated PHYceiverTM

General Description

The ICS1889 is a fully integrated physical layer device

supporting 100 Megabits per second CSMA/CD Fast

Ethernet fiber optic applications. It is designed to support

the requirements of DTEs (adapter cards), repeaters and

switches. It is compliant with the ISO/IEC 8802 Fast

Ethernet standard for 100Base-FX. It provides a Media

Independent Interface (MII) allowing direct chip-to-chip

connection, motherboard-to-daughter board connection or

connection via a cable in a similar manner to the AUI

approach used with 10Base-Tsystems. A station

management interface is provided to receive command

information and send status information. It transmits and

receives NRZI data and interfaces directly to the optical

transceiver. It can operate in either half duplex or full

duplex.

Features

One chip integrated physical layer

All CMOS, low power design

ISO/IEC 8802-3 CSMA/CD compliant

100Base-FX Half & Full Duplex

Far end fault detection

Media Independent Interface (MII)

Station management interface

Extended register set including QuickPollTM detailed

status monitoring

Transmit clock synthesis

Receive clock and data recovery

Detailed receive error reporting

Extended Test Modes

52-pin MQFP package with 2.0 mil body thickness

Block Diagram

ICS1889RevF092497P

PHYceiver and QuickPoll are trademarks of Integrated Circuit Systems, Inc.

1 page

ICS1889

4B/5B Encoder/Decoder

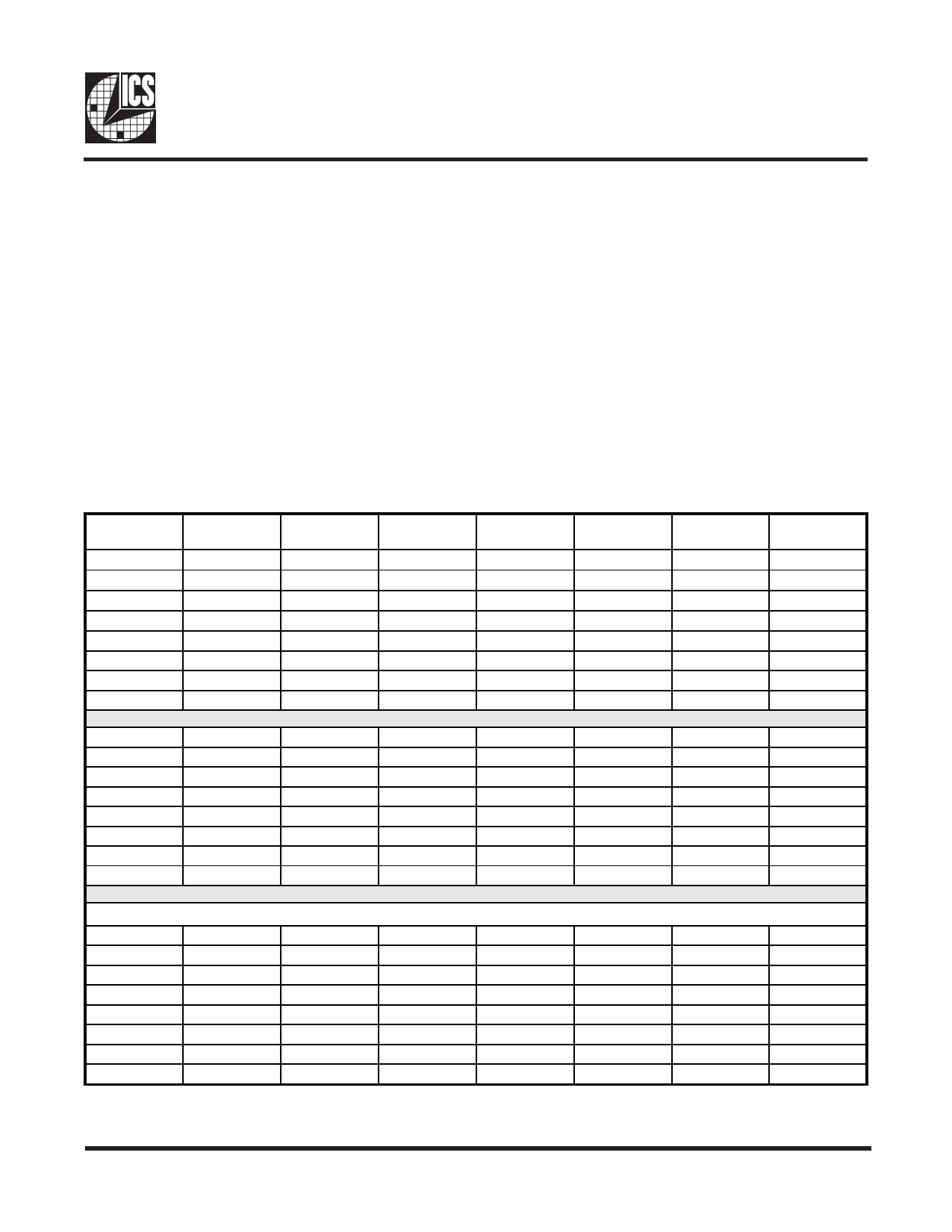

The ICS1889 uses a 4B5B coding scheme. This maps a 4-bit

nibble to a 5-bit code group called a symbol. Five bits allow

32 possible symbols, 16 are used for data encoding, 6 are used

for control and 10 are not used and are invalid. The control

symbols used are JK as the SSD, TR as the ESD, I as

the IDLE symbol and H to signal an error. All other

symbols are invalid and, if detected, will set the receive error

bit in the status register, and cause the RXER signal to be

asserted (see Table 1 below).

When transmitting, nibbles from the MII are converted to a 5-

bit code groups. During transmission, the first 16 nibbles

obtained from the MII are the MAC frame preamble.

The ICS1889 replaces the first two nibbles with the start-of-

stream delimiter (the JK symbol pair). Following the last

nibble, the ICS1889 adds the end-of-stream delimiter (the

TR symbol pair).

When receiving, 5-bit code groups are converted to nibbles

and presented to the MII. If the ICS1889 detects one or more

invalid symbols, it sets the Invalid Symbol bit (17:7) in the

QuickPoll Status Register. When receiving a frame, the first

two 5-bit code groups received are the start-of-stream

delimiter (the JK symbol pair), the ICS1889 strips them

and substitutes two nibbles of the normal preamble pattern.

The last two 5-bit code groups are the end-of-stream delimiter

(the TR symbol pair), these are stripped from the nibbles

presented to the MAC.

Symbol

0

1

2

3

4

5

6

7

Meaning

Data 0

Data 1

Data 2

Data 3

Data 4

Data 5

Data 6

Data 7

Table 1: 4B5B Encoding

4B Code

3210

0000

0001

0010

0011

0100

0101

0110

0111

5B Code

43210

11110

01001

10100

10101

01010

01011

01110

01111

Symbol

8

9

A

B

C

D

E

F

Meaning

Data 8

Data 9

Data A

Data B

Data C

Data D

Data E

Data F

4B Code

3210

1000

1001

1010

1011

1100

1101

1110

1111

5B Code

43210

10010

10011

10110

10111

11010

11011

11100

11101

I Idle

Undefined 1 1 1 1 1

V

Invalid

Undefined 0 0 0 1 0

J SSD

0101 11000

V

Invalid

Undefined 0 0 0 1 1

K SSD

0101 10001

V

Invalid

Undefined 0 0 1 0 1

T

ESD

Undefined 0 1 1 0 1

V

Invalid

Undefined 0 0 1 1 0

R

ESD

Undefined 0 0 1 1 1

V

Invalid

Undefined 0 1 0 0 0

H

Error

Undefined 0 0 1 0 0

V

Invalid

Undefined 0 1 1 0 0

V

Invalid

Undefined 0 0 0 0 0

V

Invalid

Undefined 1 0 0 0 0

V

Invalid

Undefined 0 0 0 0 1

V

Invalid

Undefined 1 1 0 0 1

Invalid Error Code Test TXER asserted

I Idle

1 1 1 1 1 1 1 1 1 V Invalid 0 0 1 0

J SSD

1 1 1 0 1 1 0 0 0 V Invalid 0 0 1 1

K SSD

1 0 1 1 1 0 0 0 1 V Invalid 0 1 0 1

T ESD

1 0 0 1 0 1 1 0 1 V Invalid 0 1 1 0

R ESD

0 1 1 1 0 0 1 1 1 V Invalid 1 0 0 0

H Error

0 1 0 0 0 0 1 0 0 V Invalid 1 0 1 0

V Invalid 0 0 0 0 0 0 0 0 0 V Invalid 1 1 0 0

V Invalid 0 0 0 1 0 0 0 0 1 V Invalid 1 1 0 1

1. The IDLE symbol is sent continuously between frames.

2. J and K are the SSD and are always sent in pairs.

3. K always follows J.

4. T and R are the ESD and are always sent in pairs.

5. R always follows T.

6. A HALT symbol is used to signal an error condition.

00010

00011

00101

00110

01000

01100

10000

11001

5

5 Page

Link Status (bit 2)

When set to a logic one, this bit indicates that the Link

Monitor has established a valid link. If the Link Monitor

detects a link failure, this bit is set to a logic zero and remains

zero through the next read of the status register. A link failure

may be due to an error in the receive channel or an error in the

receive channel of the link partner (that is, a remote fault).

Jabber detect (bit 1)

This bit is permanently set to a logic zero.

Extended Capability (bit 0)

This bit is permanently set to a logic one indicating that the

ICS1889 has an extended register set.

ICS1889

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ICS1889.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS1886 | FDDI / Fast Ethernet PHYceiverTM | Integrated Circuit Systems |

| ICS1887 | FDDI / Fast Ethernet PHYceiverTM | Integrated Circuit Systems |

| ICS1889 | 100Base-FX Integrated PHYceiverTM | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |