Philips Semiconductors

Cordless telephone line interface

Objective specification

UBA1706

PINNING

SYMBOL PIN

DESCRIPTION

LN 1 positive line terminal

REG

2 line voltage regulator decoupling

LVI 3 negative line voltage sense input

RGL

4 reference for current regulation mode

LCC

5 line current control output

CST

6 input for stability capacitor

RXO

7 receive amplifier output

AGC

8 automatic gain control/line loss

compensation adjustment

RXI 9 receiver amplifier input

EHI 10 electronic hook switch control input

DATA

11 serial bus data input

EN 12 programming serial bus enable input

CLK 13 serial bus clock input

TXI−

TXI+

14 inverted transmit amplifier input

15 non-inverted transmit amplifier input

n.c. 16 not connected

SWI2

17 NPN open-collector output 2

SWI1

18 NPN open-collector output 1

GND

19 ground reference

n.c. 20 not connected

VCC 21 supply voltage

n.c. 22 not connected

n.c. 23 not connected

SLPE

24 connection for slope resistor

handbook, halfpage

LN 1

24 SLPE

REG 2

23 n.c.

LVI 3

22 n.c.

RGL 4

LCC 5

21 VCC

20 n.c.

CST 6

RXO 7

19 GND

UBA1706

18 SW1

AGC 8

17 SW2

RXI 9

16 n.c.

EHI 10

15 TXI+

DATA 11

14 TXI-

EN 12

13 CLK

FCA031

Fig.2 Pin configuration.

1999 Jun 04

5

Philips Semiconductors

Cordless telephone line interface

Objective specification

UBA1706

Input EHI can also be used for pulse dialling or register

recall (timed loop break). During line breaks (the voltage at

pin EHI is LOW or open-circuit), the voltage regulator is

switched off and the capacitor at pin REG is internally

disconnected to prevent its discharge. As a result, the

voltage stabilizer will have negligible switch-on delay after

line interruptions. This minimizes the contribution of the IC

to the current waveform during pulse dialling or register

recall.

When the UBA1706 is in power-down mode (bit PD at

logic 1), transistor TPDARL is forced off whatever the

voltage applied at pin EHI.

The rail-to-rail output stage is designed to drive a 500 µA

peak current. The output impedance at pin RXO is

approximately 100 Ω.

The voltage gain from pin RXI to pin RXO is set at 37.9 dB.

This gain value compensates typically the attenuation of

the anti-sidetone network (see Fig.10). The output and the

input are biased at 2 × Vd ≅ 1.4 V.

AGC is provided on this amplifier for line loss

compensation. This amplifier can be muted by activating

the receive mute function (bit RXM at logic 1).

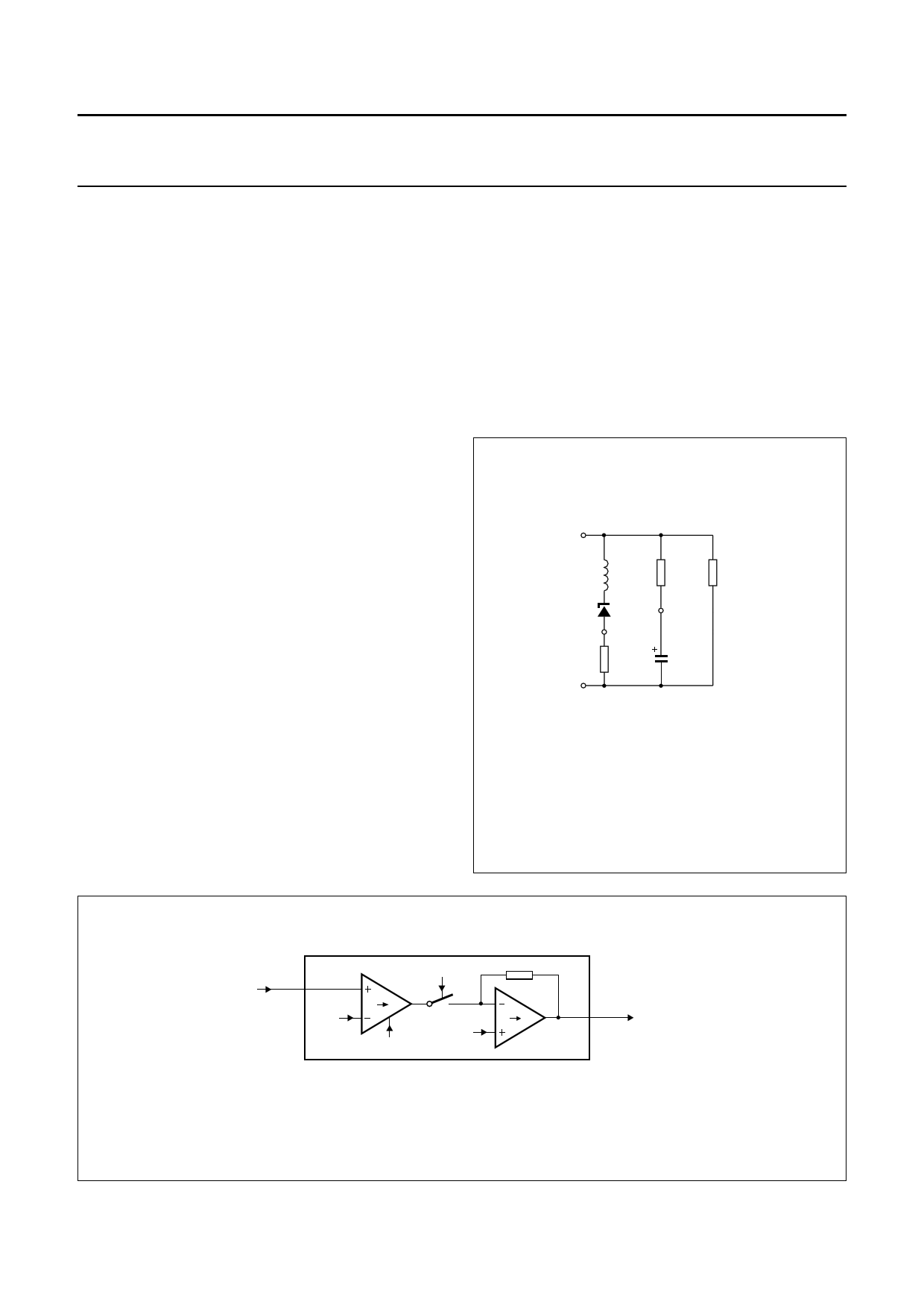

SET IMPEDANCE

In the audio frequency range, the dynamic impedance

between pins LN and GND (illustrated in Fig.8) is mainly

determined by the ZSET impedance. The impedance

introduced by the external TNSW transistor connected

between pins GND and LN− is negligible.

TRANSMIT AMPLIFIER (PINS TXI+ AND TXI−)

The UBA1706 has symmetrical transmit inputs TXI+ and

TXI−. The input impedance between pins TXI+ or TXI− and

GND is 21 kΩ. The voltage gain from pins TXI+ or TXI− to

pin LN is set at 11.6 dB with 600 Ω line load (Zline) and

619 Ω set impedance. The inputs are biased at

2 × Vd ≅ 1.4 V, with Vd representing the diode voltage.

AGC is provided on this amplifier for line loss

compensation.

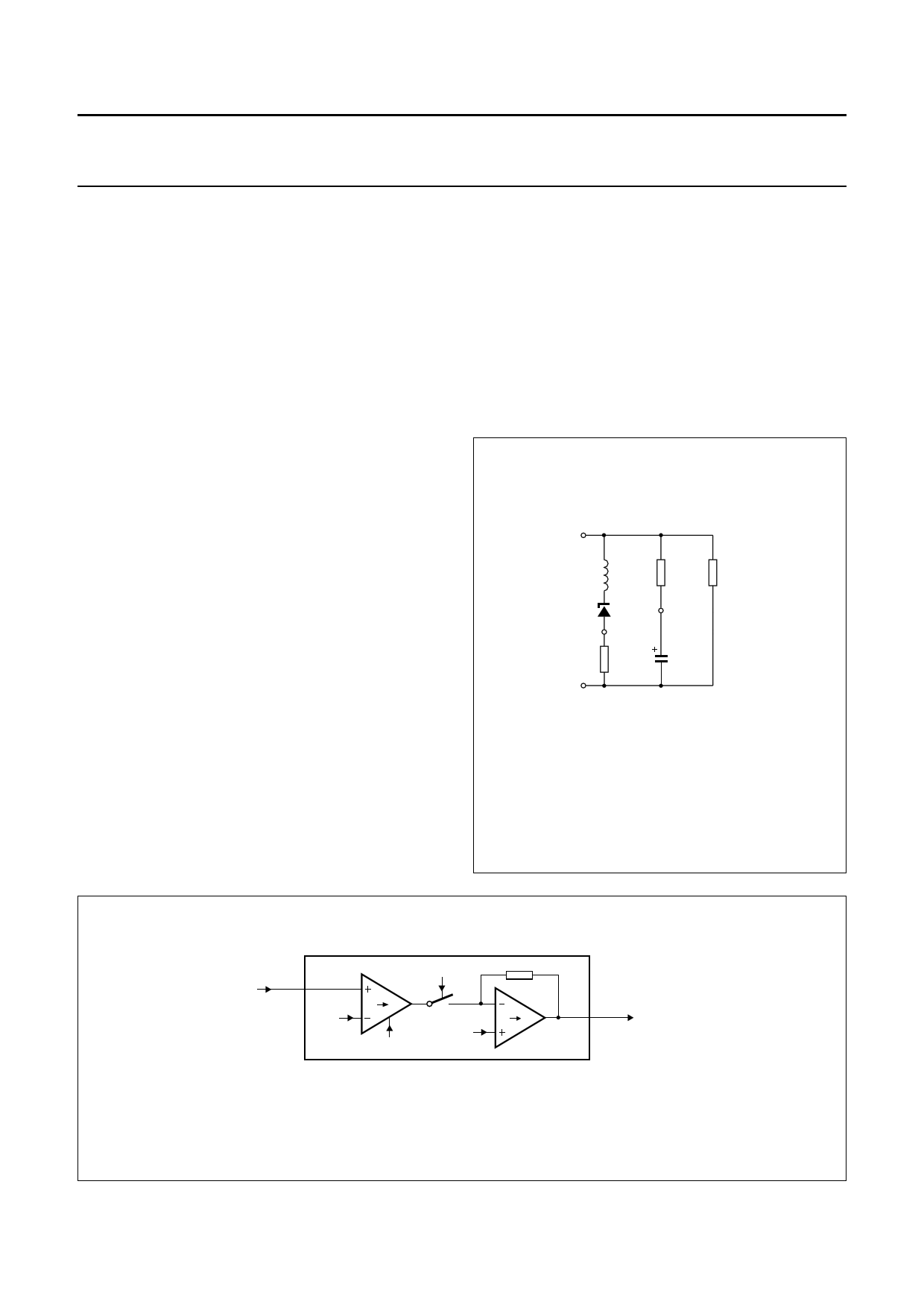

RECEIVE AMPLIFIER (PINS RXI AND RXO; BIT RXM)

The receive amplifier (see Fig.9) has one input (RXI) and

one output (RXO). The input impedance between

pins RXI and GND is 21 kΩ.

handbook, halfpage LN

LEQ

RP

ZSET

619 Ω

Vref

SLPE

GND

RSLPE

10 Ω

REG

CREG

4.7 µF

MGL215

Leq = CREG × RSLPE × RP

RP = internal resistance = 35 kΩ.

Fig.8 Equivalent impedance between

pins LN and GND.

handbook, full pagewidth

RXI

2Vd

RXM

VI

from AGC

2Vd

IV

RXO

UBA1706

FCA035

Bit names are given in italics.

Fig.9 Receive amplifier.

1999 Jun 04

11