|

|

PDF ICS601G-01IT Data sheet ( Hoja de datos )

| Número de pieza | ICS601G-01IT | |

| Descripción | LOW PHASE NOISE CLOCK MULTIPLIER | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS601G-01IT (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

ICS601-01

LOW PHASE NOISE CLOCK MULTIPLIER

Description

The ICS601-01 is a low-cost, low phase noise,

high-performance clock synthesizer for applications

which require low phase noise and low jitter. It is ICS’

lowest phase noise multiplier, and also the lowest

CMOS part in the industry. Using ICS’ patented

analong and digital Phase-Locked Loop (PLL)

techniques, the chip accepts a 10 - 27 MHz crystal or

clock input, and produces output clocks up to 156 MHz

at 3.3 V.

This product is intended for clock generation. It has low

output jitter (variation in the output period), but input

and output skew and jitter are not defined nor

guaranteed. For applications which require definted

input to output timing, use the ICS670-01.

Features

• Packaged in 16-pin SOIC or TSSOP

• Available in Pb (lead) free package

• Uses fundamental 10 - 27 MHz crystal or clock

• Patented PLL with the lowest phase noise

• Output clocks up to 156 MHz at 3.3 V

• Low phase noise: -132 dBc/Hz at 10 kHz

• Low jitter - 18 ps one sigma typ.

• Full swing CMOS outputs with 25 mA drive capability

at TTL levels

• Advanced, low power, sub-micron CMOS process

• Industrial temperature range available

• Operating voltage of 3.3V or 5V

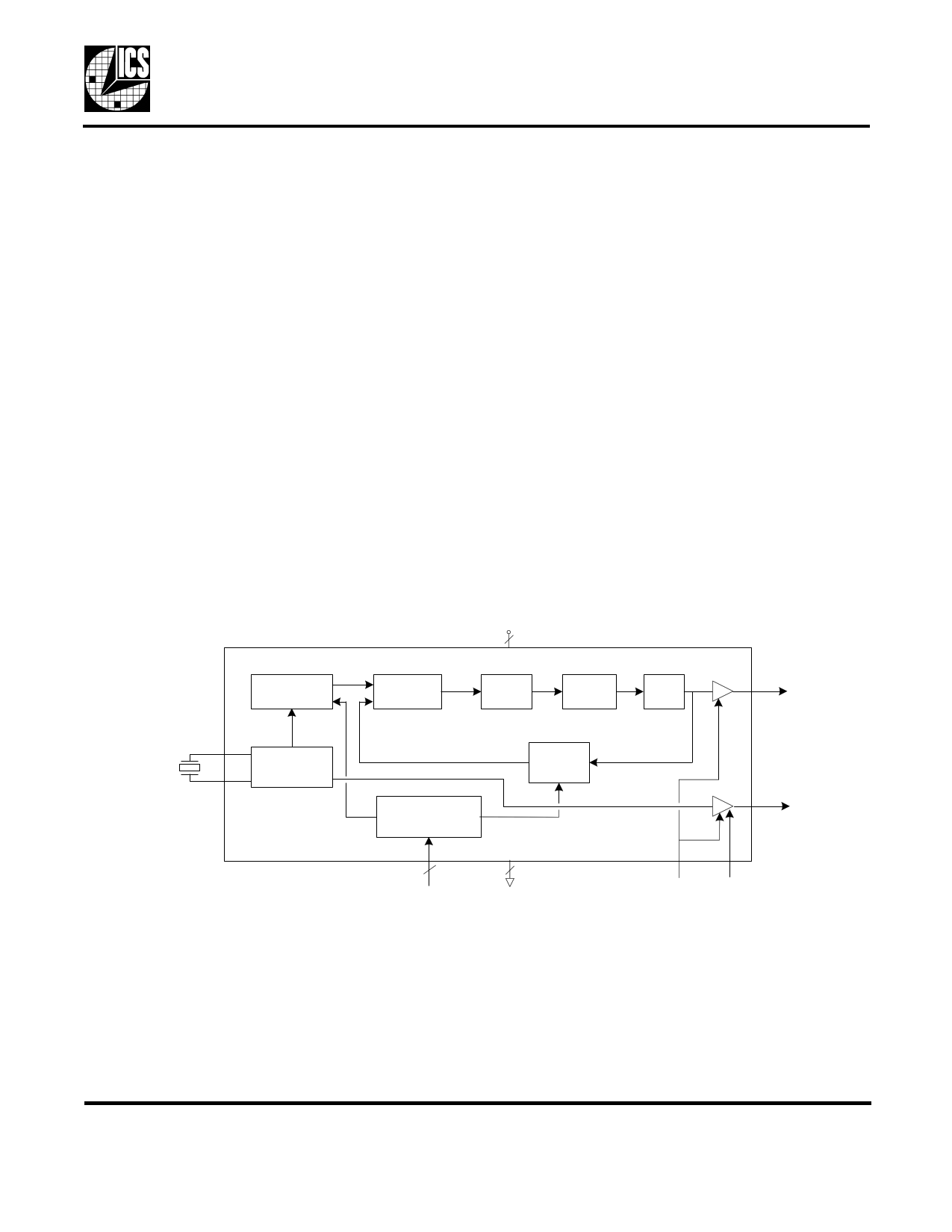

Block Diagram

X1/ICLK

Crystal or

clock input

X2

Reference

Divider

Crystal

Oscillator

Phase

Comparator

VDD

3

Charge

Pump

Loop

Filter

VCO

CLK

ROM Based

Multipliers

VCO

Divide

4

S3:0

3

GND

REFOUT

OE REFEN

MDS 601-01 L

1

Revision 111204

Integrated Circuit Systems ● 525 Race Street, San Jose, CA 95126 ● tel (408) 297-1201 ● www.icst.com

1 page

ICS601-01

LOW PHASE NOISE CLOCK MULTIPLIER

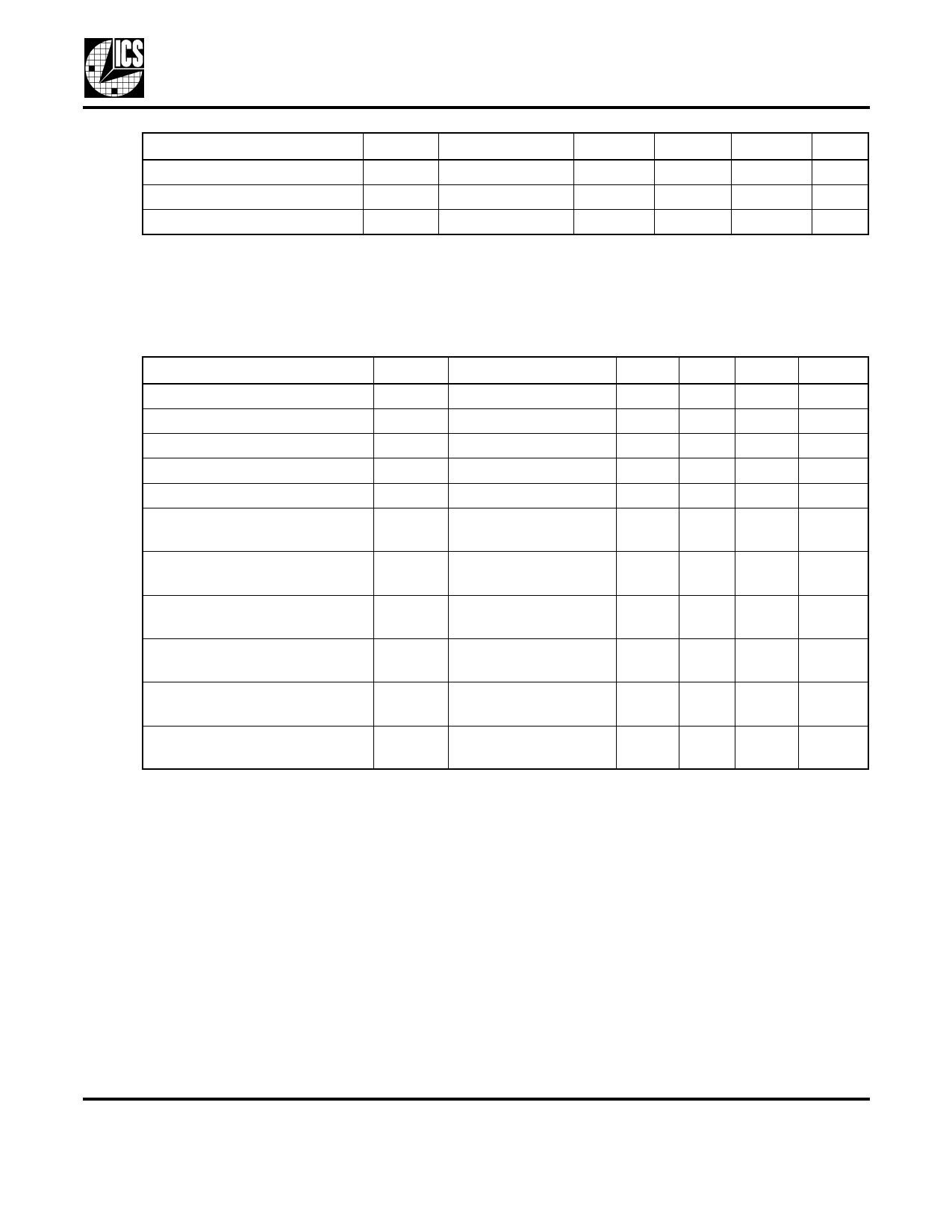

Parameter

Symbol Conditions

Operating Supply Current

IDD No load, 125 MHz

Short Circuit Current

Each output

Input Capacitance

CIN OE, select pins

Note 1: Switching occurs nominally at VDD/2

Min.

±40

Typ.

22

±60

5

Max.

30

Units

mA

mA

pF

AC Electrical Characteristics

VDD = 3.3V ±10%, Ambient Temperature -40 to +85° C

Parameter

Symbol

Conditions

Min. Typ. Max. Units

Input Frequency

Fin

10 27 MHz

Output Frequency

at 3.3V or 5V

156 MHz

Output Rise Time

Output Fall Time

Output Clock Duty Cycle

tOR 0.8 to 2.0V no load

tOF 0.8 to 2.0V, no load

at VDD/2

1.5

1.5

45 50 55

ns

ns

%

Maximum Absolute jitter, short

term, 125 MHz

No load

±50 ±75

ps

Maximum jitter, one sigma,

125 MHz (x5)

No load

12 20

ps

Phase Noise, relative to carrier,

125 MHz (x5)

100 Hz offset

-90 -94

dBc/Hz

Phase Noise, relative to carrier,

125 MHz (x5)

1 kHz

-116 -120

dBc/Hz

Phase Noise, relative to carrier,

125 MHz (x5)

10 kHz offset

-118 -122

dBc/Hz

Phase Noise, relative to carrier,

125 MHz (x5)

100 kHz offset

-115 -119

dBc/Hz

Note 2: Input frequency limited by maximum output frequency and multiplication factor (I.e. For 16x,

maximum input frequency is 13.75 MHz).

MDS 601-01 L

5

Revision 111204

Integrated Circuit Systems ● 525 Race Street, San Jose, CA 95126 ● tel (408) 297-1201 ● www.icst.com

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet ICS601G-01IT.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS601G-01ILFT | LOW PHASE NOISE CLOCK MULTIPLIER | Integrated Circuit Systems |

| ICS601G-01IT | LOW PHASE NOISE CLOCK MULTIPLIER | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |