|

|

PDF ATtiny28L-4PC Data sheet ( Hoja de datos )

| Número de pieza | ATtiny28L-4PC | |

| Descripción | 8-bit AVR Microcontroller with 2K Bytes of Flash | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ATtiny28L-4PC (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

Features

• Utilizes the AVR® RISC Architecture

• AVR – High-performance and Low-power RISC Architecture

– 90 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General-purpose Working Registers

– Up to 4 MIPS Throughput at 4 MHz

• Nonvolatile Program Memory

– 2K Bytes of Flash Program Memory

– Endurance: 1,000 Write/Erase Cycles

– Programming Lock for Flash Program Data Security

• Peripheral Features

– Interrupt and Wake-up on Low-level Input

– One 8-bit Timer/Counter with Separate Prescaler

– On-chip Analog Comparator

– Programmable Watchdog Timer with On-chip Oscillator

– Built-in High-current LED Driver with Programmable Modulation

• Special Microcontroller Features

– Low-power Idle and Power-down Modes

– External and Internal Interrupt Sources

– Power-on Reset Circuit with Programmable Start-up Time

– Internal Calibrated RC Oscillator

• Power Consumption at 1 MHz, 2V, 25°C

– Active: 3.0 mA

– Idle Mode: 1.2 mA

– Power-down Mode: <1 µA

• I/O and Packages

– 11 Programmable I/O Lines, 8 Input Lines and a High-current LED Driver

– 28-lead PDIP, 32-lead TQFP, and 32-pad MLF

• Operating Voltages

– VCC: 1.8V - 5.5V for the ATtiny28V

– VCC: 2.7V - 5.5V for the ATtiny28L

• Speed Grades

– 0 - 1.2 MHz for the ATtiny28V

– 0 - 4 MHz For the ATtiny28L

Pin Configurations

PDIP

TQFP/MLF

RESET

PD0

PD1

PD2

PD3

PD4

VCC

GND

XTAL1

XTAL2

PD5

PD6

PD7

(AIN0) PB0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28 PA0

27 PA1

26 PA3

25 PA2 (IR)

24 PB7

23 PB6

22 GND

21 NC

20 VCC

19 PB5

18 PB4 (INT1)

17 PB3 (INT0)

16 PB2 (T0)

15 PB1 (AIN1)

PD3

PD4

NC

VCC

GND

NC

XTAL1

XTAL2

1

2

3

4

5

6

7

8

24 PB7

23 PB6

22 NC

21 GND

20 NC

19 NC

18 VCC

17 PB5

8-bit

Microcontroller

with 2K Bytes of

Flash

ATtiny28L

ATtiny28V

Rev. 1062E–10/01

1

1 page

External Clock

ATtiny28L/V

To drive the device from an external clock source, XTAL2 should be left unconnected

while XTAL1 is driven as shown in Figure 3.

Figure 3. External Clock Drive Configuration

NC

EXTERNAL

OSCILLATOR

SIGNAL

XTAL2

XTAL1

GND

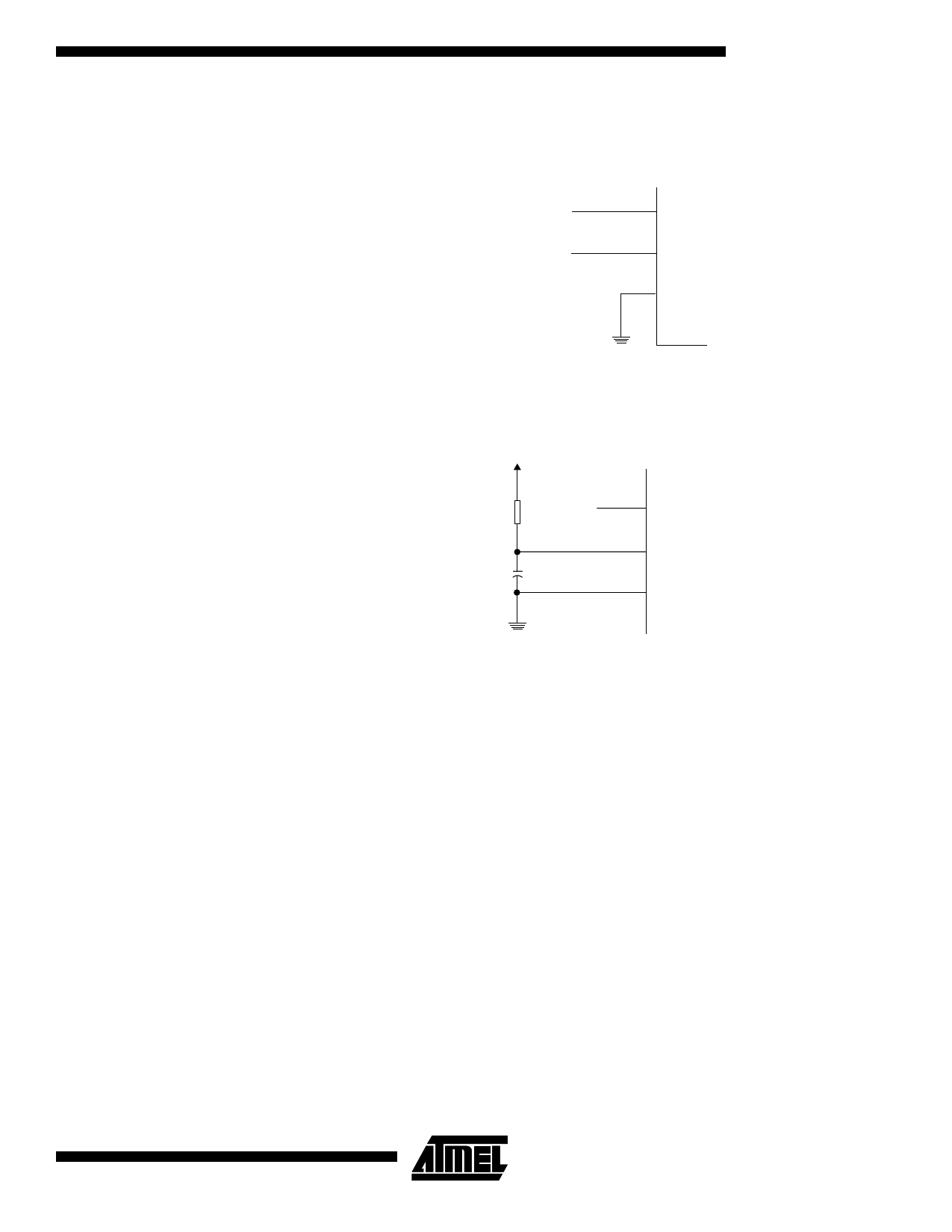

External RC Oscillator

For timing insensitive applications, the external RC configuration shown in Figure 4 can

be used. For details on how to choose R and C, see Table 25 on page 54.

Figure 4. External RC Configuration

VCC

R NC XTAL2

XTAL1

C

GND

1062E–10/01

5

5 Page

I/O Memory

Status Register – SREG

ATtiny28L/V

The I/O space definition of the ATtiny28 is shown in Table 2.

Table 2. ATtiny28 I/O Space

Address Hex Name

Function

$3F

SREG

Status Register

$1B

PORTA

Data Register, Port A

$1A

PACR

Port A Control Register

$19 PINA Input Pins, Port A

$16 PINB Input Pins, Port B

$12

PORTD

Data Register, Port D

$11

DDRD

Data Direction Register, Port D

$10 PIND Input Pins, Port D

$08

ACSR

Analog Comparator Control and Status Register

$07

MCUCS

MCU Control and Status Register

$06 ICR

Interrupt Control Register

$05 IFR

Interrupt Flag Register

$04

TCCR0

Timer/Counter0 Control Register

$03

TCNT0

Timer/Counter0 (8-bit)

$02

MODCR

Modulation Control Register

$01

WDTCR

Watchdog Timer Control Register

$00 OSCCAL Oscillator Calibration Register

Note: Reserved and unused locations are not shown in the table.

All ATtiny28 I/O and peripherals are placed in the I/O space. The I/O locations are

accessed by the IN and OUT instructions transferring data between the 32 general-pur-

pose working registers and the I/O space. I/O registers within the address range $00 -

$1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the

value of single bits can be checked by using the SBIS and SBIC instructions. Refer to

the Instruction Set section for more details.

For compatibility with future devices, reserved bits should be written to zero if accessed.

Reserved I/O memory addresses should never be written.

The I/O and peripherals control registers are explained in the following sections.

The AVR status register (SREG) at I/O space location $3F is defined as:

Bit

$3F

Read/Write

Initial Value

7

I

R/W

0

6

T

R/W

0

5

H

R/W

0

4

S

R/W

0

3

V

R/W

0

2

N

R/W

0

1

Z

R/W

0

0

C SREG

R/W

0

• Bit 7 – I: Global Interrupt Enable

The global interrupt enable bit must be set (one) for the interrupts to be enabled. The

individual interrupt enable control is then performed in separate control registers. If the

global interrupt enable register is cleared (zero), none of the interrupts are enabled inde-

pendent of the individual interrupt enable settings. The I-bit is cleared by hardware after

1062E–10/01

11

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet ATtiny28L-4PC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ATtiny28L-4PC | 8-bit AVR Microcontroller with 2K Bytes of Flash | ATMEL Corporation |

| ATtiny28L-4PI | 8-bit AVR Microcontroller with 2K Bytes of Flash | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |