|

|

PDF WF57ETIBCDC0 Data sheet ( Hoja de datos )

| Número de pieza | WF57ETIBCDC0 | |

| Descripción | C/CONT+TOUCH | |

| Fabricantes | SYC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de WF57ETIBCDC0 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

SPECIFICATION

CUSTOMER :

MODULE NO.: WF57ETIBCDC0

PANTALLA TFT 5.7" C/CONT+TOUCH

APPROVED BY:

( FOR CUSTOMER USE ONLY )

PCB VERSION:

DATA:

SALES BY

APPROVED BY

CHECKED BY

PREPARED BY

VERSION

A

DATE

REVISED

SUMMARY

PAGE NO.

2011.01.10 9~16 Correct DC Characteristics &

AC Characteristics &Data

transfer order Setting

1 31

www.sycelectronica.com.ar

1 page

This product is composed of a TFT LCD panel, driver ICs,

FPC, Control Board and a backlight unit. The following table

described the features of WF57ETIBCDC#001.

Item

Dot Matrix

Module dimension

View area

Dot pitch

Driving IC package

LCD type

View direction

Backlight Type

Controller IC

Dimension

320 x RGBx240(TFT)

141.12x 101.55 x 7.8 (max)

126.0x 89.1

0.12 x 0.36

COG

TFT, Negative, Transmissive

6 o’clock

LED,Normally White

SSD1963

Unit

dots

mm

mm

mm

*Expose the IC number blaze (Luminosity over than 1 cd) when using the LCM may cause IC operating

failure.

*Color tone slight changed by temperature and driving voltage.

5 31

www.sycelectronica.com.ar

5 Page

7.2 MCU Interface Timing

7.2.1 Parallel 6800-series Interface Timing

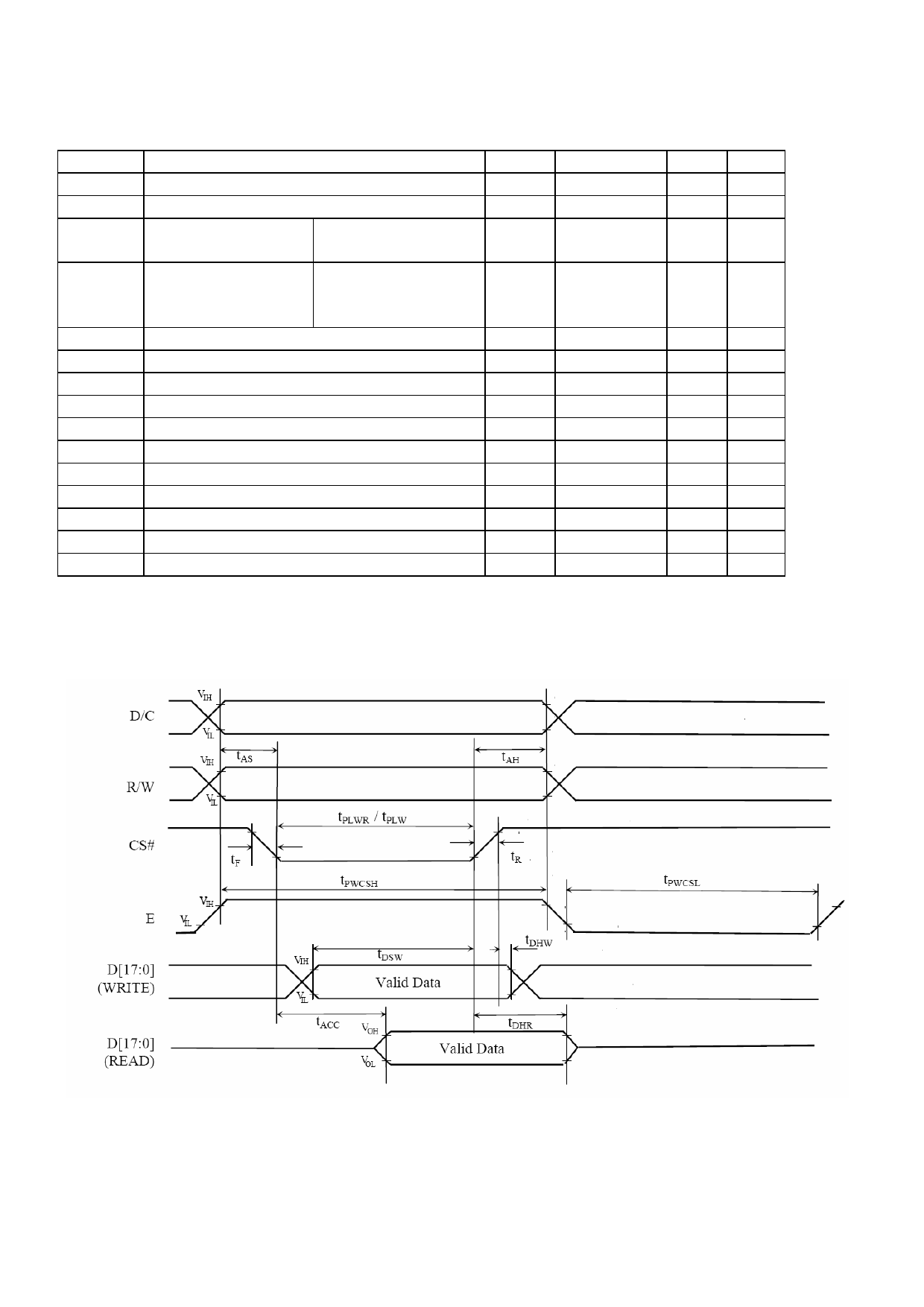

Table 7-4: Parallel 6800-series Interface Timing Characteristics (Use CS# as clock)

Symbol Parameter

Min Typ Max Unit

fMCLK System Clock Frequency*

tMCLK System Clock Period*

1

1/ fMCLK

-

-

110 MHz

- ns

tPWCSH

Control Pulse High

Width

Write

Read

13

30

1.5* tMCLK

3.5* tMCLK

-

ns

tPWCSL

tAS

tAH

Control Pulse Low

Width

Address Setup Time

Address Hold Time

Write (next write cycle)

Write (next read cycle)

Read

13 1.5* tMCLK

80 9* tMCLK -

80 9* tMCLK

2 --

2 --

ns

ns

ns

tDSW Data Setup Time

4 - - ns

tDHW Data Hold Time

1 - - ns

tPLW

tPHW

tPLWR

Write Low Time

Write High Time

Read Low Time

14 - - ns

14 - - ns

38 - - ns

tACC Data Access Time

32 - - ns

tDHR Output Hold time

1 - - ns

tR Rise Time

- - 0.5 ns

tF Fall Time

- - 0.5 ns

* System Clock denotes external input clock (PLL-bypass) or internal generated clock (PLL-enabled)

Figure 7-1: Parallel 6800-series Interface Timing Diagram (Use CS# as Clock)

11 31

www.sycelectronica.com.ar

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet WF57ETIBCDC0.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| WF57ETIBCDC0 | C/CONT+TOUCH | SYC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |