|

|

PDF X28HC256 Data sheet ( Hoja de datos )

| Número de pieza | X28HC256 | |

| Descripción | Byte Alterable E2PROM | |

| Fabricantes | Xicor | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de X28HC256 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

X28HC256

256K

X28HC256

5 Volt, Byte Alterable E2PROM

32K x 8 Bit

FEATURES

• Access Time: 70ns

• Simple Byte and Page Write

—Single 5V Supply

— No External High Voltages or VPP Control

Circuits

— Self-Timed

— No Erase Before Write

— No Complex Programming Algorithms

—No Overerase Problem

• Low Power CMOS:

—Active: 60mA

—Standby: 500µA

• Software Data Protection

—Protects Data Against System Level

Inadvertent Writes

• High Speed Page Write Capability

• Highly Reliable Direct Write™ Cell

—Endurance: 100,000 Write Cycles

—Data Retention: 100 Years

• Early End of Write Detection

—DATA Polling

—Toggle Bit Polling

PIN CONFIGURATION

DESCRIPTION

The X28HC256 is a second generation high perfor-

mance CMOS 32K x 8 E2PROM. It is fabricated with

Xicor’s proprietary, textured poly floating gate tech-

nology, providing a highly reliable 5 Volt only nonvolatile

memory.

The X28HC256 supports a 128-byte page write opera-

tion, effectively providing a 24µs/byte write cycle and

enabling the entire memory to be typically rewritten in

less than 0.8 seconds. The X28HC256 also features

DATA Polling and Toggle Bit Polling, two methods of

providing early end of write detection. The X28HC256

also supports the JEDEC standard Software Data Pro-

tection feature for protecting against inadvertent writes

during power-up and power-down.

Endurance for the X28HC256 is specified as a minimum

100,000 write cycles per byte and an inherent data

retention of 100 years.

PLASTIC DIP

CERDIP

FLAT PACK

SOIC

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O0

I/O1

I/O2

VSS

1 28

2 27

3 26

4 25

5 24

6 23

7 22

X28HC256

8 21

9 20

10 19

11 18

12 17

13 16

14 15

VCC

WE

A13

A8

A9

A11

OE

A10

CE

I/O7

I/O6

I/O5

I/04

I/O3

3859 FHD F02

LCC

PLCC

4 3 2 1 32 31 30

A6 5

29 A8

A5 6

28 A9

A4 7

27 A11

A3 8

A2 9

X28HC256

26 NC

25 OE

A1 10

24 A10

A0 11

23 CE

NC 12

22 I/O7

I/O0 13

21 I/O6

14 15 16 17 18 19 20

3859 FHD F03

A2

A1

A0

I/O0

I/O1

I/O2

NC

VSS

NC

I/O3

I/O4

I/O5

I/O6

I/O7

CE

A10

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

TSOP

X28HC256

32 A3

31 A4

30 A5

29 A6

28 A7

27 A12

26 A14

25 NC

24 VCC

23 NC

22 WE

21 A13

20 A8

19 A9

18 A11

17 OE

3859 ILL F22

©Xicor, Inc. 1991, 1995 Patents Pending

3859-2.8 8/5/97 T1/C0/D0 EW

1 Characteristics subject to change without notice

1 page

X28HC256

THE TOGGLE BIT I/O6

Figure 4. Toggle Bit Bus Sequence

LAST

WE WRITE

CE

OE

VOH

I/O6 * VOL

* I/O6 beginning and ending state of I/O6 will vary.

Figure 5. Toggle Bit Software Flow

LAST WRITE

YES

LOAD ACCUM

FROM ADDR n

HIGH Z

*

X28HC256

READY

3859 FHD F14

The Toggle Bit can eliminate the software housekeeping

chore of saving and fetching the last address and data

written to a device in order to implement DATA Polling.

This can be especially helpful in an array comprised of

multiple X28HC256 memories that is frequently up-

dated. The timing diagram in Figure 4 illustrates the

sequence of events on the bus. The software flow

diagram in Figure 5 illustrates a method for polling the

Toggle Bit.

COMPARE

ACCUM WITH

ADDR n

COMPARE

OK?

YES

X28HC256

READY

NO

3859 FHD F15

5

5 Page

X28HC256

POWER-UP TIMING

Symbol

tPUR(3)

tPUW(3)

Parameter

Power-Up to Read

Power-Up to Write

Max.

100

5

Units

µs

ms

3859 PGM T05

CAPACITANCE TA = +25°C, f = 1MHz, VCC = 5V.

Symbol

Test

CI/O(9)

CIN(9)

Input/Output Capacitance

Input Capacitance

Max.

10

6

Units

pF

pF

Conditions

VI/O = 0V

VIN = 0V

3859 PGM T06.2

ENDURANCE AND DATA RETENTION

Parameter

Endurance

Data Retention

Min.

100,000

100

Max.

Units

Cycles

Years

3859 PGM T07.3

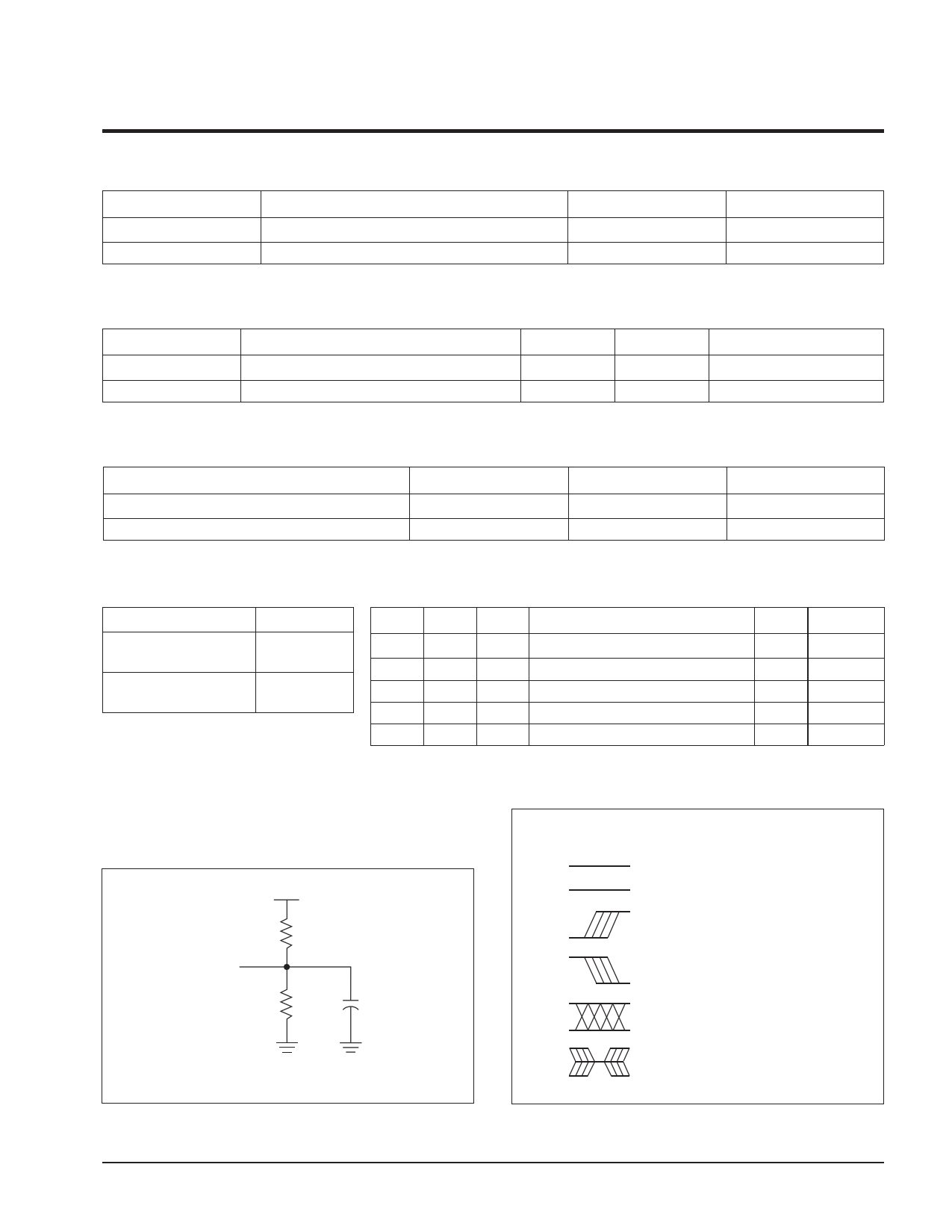

A.C. CONDITIONS OF TEST

Input Pulse Levels

Input Rise and

Fall Times

Input and Output

Timing Levels

0V to 3V

5ns

1.5V

3859 PGM T08.1

MODE SELECTION

CE OE WE

L LH

LHL

HXX

XLX

XXH

Mode

Read

Write

Standby and Write Inhibit

Write Inhibit

Write Inhibit

I/O Power

DOUT

DIN

High Z

—

—

Active

Active

Standby

—

—

3859 PGM T09

Note: (3) This parameter is periodically sampled and not 100%

tested.

EQUIVALENT A.C. LOAD CIRCUIT

5V

OUTPUT

1.92KΩ

1.37KΩ

30pF

3859 FHD F20.3

SYMBOL TABLE

WAVEFORM INPUTS

OUTPUTS

Must be

steady

May change

from LOW

to HIGH

May change

from HIGH

to LOW

Don’t Care:

Changes

Allowed

N/A

Will be

steady

Will change

from LOW

to HIGH

Will change

from HIGH

to LOW

Changing:

State Not

Known

Center Line

is High

Impedance

11

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet X28HC256.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| X28HC256 | Byte Alterable E2PROM | Xicor |

| X28HC256 | Byte Alterable EEPROM | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |