|

|

PDF BU9408KS2 Data sheet ( Hoja de datos )

| Número de pieza | BU9408KS2 | |

| Descripción | 32bit Audio DSP | |

| Fabricantes | ROHM Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de BU9408KS2 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Digital Sound Processors for FPD TVs

32bit Audio DSP with Built-in 4ch

DAC and ASRC

BU9408KS2

No.12083EAT02

●General Description

This LSI is the digital sound processor which made

the use digital signal processing for FPD TVs.

DSP of ROHM original is used for the TV sound processor unit, and it excels in cost performance. A selection input of two

lines is possible from four digital inputs. An asynchronous sampling rate converter(ASRC) is built in one line. Three digital

outputs are built in.

Two audio DA converters are built in.

●Features

■Digital Signal Processor unit

Word length:

32bit (Data RAM)

The fastest machine cycle: 40.7ns (512fs, fs = 48kHz)

Multiplier:

32 x 24 → 56bit

Adder:

32 + 32 → 32bit

Data RAM:

256 x 32bit

Coefficient RAM:

128 x 24bit

Sampling frequency:

fs = 48kHz

Master clock :

512fs(24.576MHz,fs=48kHz)

■Digital signal input (Stereo4lines):

16/20/24bit (I2S, Left-Justified, Right-Justified)

Digital signal output (Stereo 3 lines):

16/20/24bit (I2S, Left-Justified, Right-Justified, S/PDIF)

■.Asynchronous sampling rate converter

(one line at stereo):32kHz/44.1kHz/48kHz/88.2kHz/96kHz/176.4kHz/192kHz → 48kHz

■Audio DAC:One stereo output

24bit 8 x Over-sampling digital filter + 1 bit delta sigma DAC

S/N: 96dB

THD+N: 0.005%(Sine-wave 1kHz,0dB)

■Audio 16bit DAC:One stereo output

24bit 8 x Over-sampling digital filter + Audio 16bit DAC

S/N: 90dB

THD+N: 0.03%(Sine-wave 1kHz,0dB)

■The sound signal processing function for FPD TVs

Pre-Scaler, DC cut HPF, Channel Mixer, P2Volume(Perfect Pure Volume), BASS, MIDDLE,

TREBLE, Simulated-Stereo, Surround, P2Bass, P2Treble, 7Band Parametric EQ,

Master Volume, L/R balance, Post-Scaler, Output signal clipper

(P2Volume, P2Bass, and P2Treble are the sound effect functions of ROHM original.)

●Applications

Flat Panel TVs (LCD, Plasma)

www.rohm.com

© 2012 ROHM Co., Ltd. All rights reserved.

1/53

2012.03 - Rev.A

1 page

BU9408KS2

Technical Note

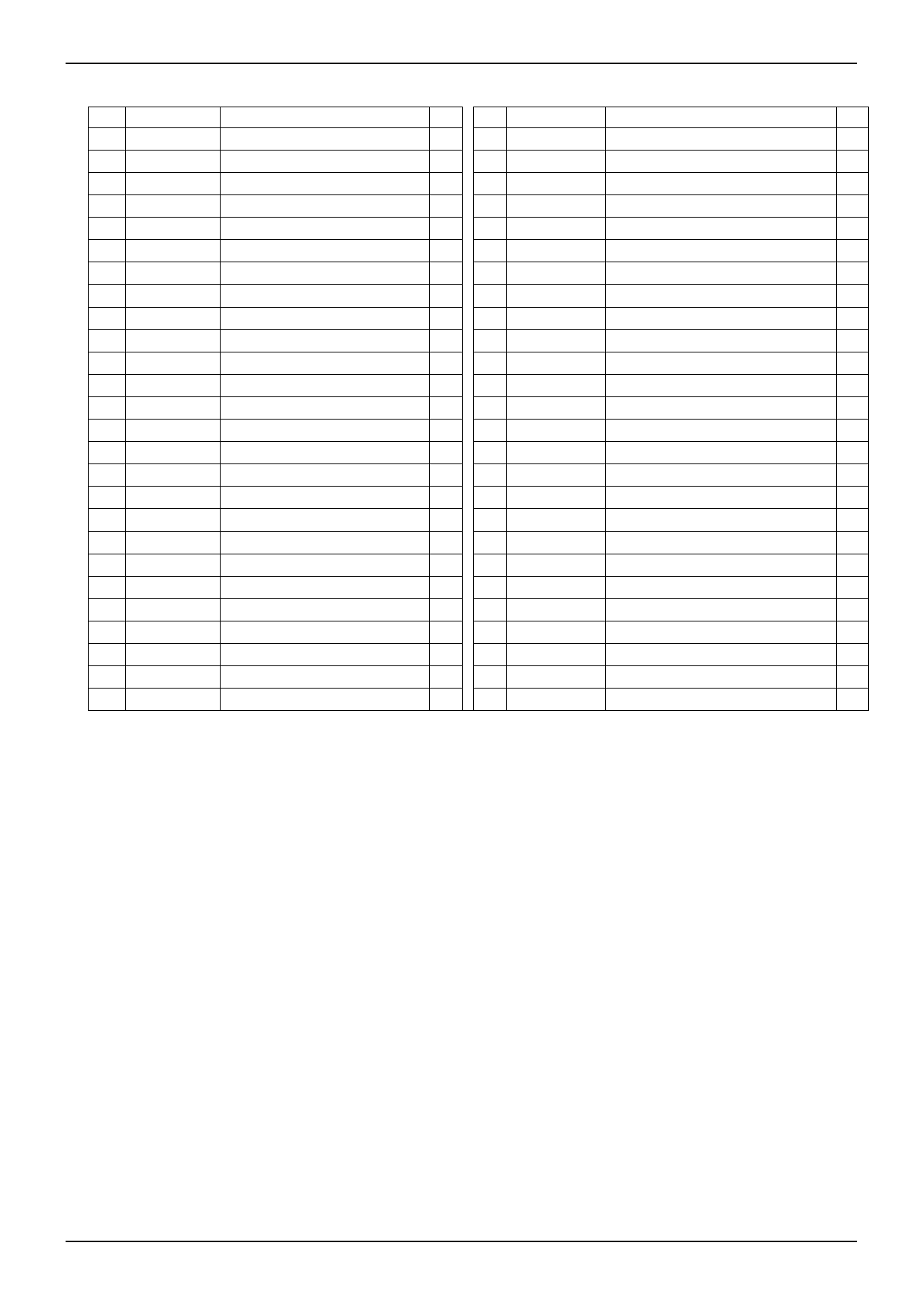

●Pin Description(s)

No. Name

1 DVDDPLL

2 FILT1

3 DGNDPLL

4 FILT2

5 SCANTEST

6 I2CADR

7 SCL

8 SDA

9 DGNDIO1

10 RESETB

11 DVDDCOR1

12 MUTE1B

13 MUTE2B

14 MUTE3B

15 AGNDDA1

16 AOUTR1

17 AOUTL1

18 AVDDDA1

19 AVDDDA2

20 AOUTR2

21 VREFDA

22 AOUTL2

23 AGNDDA2

24 ERR1_LRC

25 ERR2_BCK

26 DATASO

Description of terminals

Power supply for PLL

Type

-

PLLA filter connect terminal 1 G

GND for PLL

-

PLLA filter connect terminal 2 G

Test mode select pin

I2C slave address select pin

I2C transfer clock input pin

I2C data I/O pin

A

B

I

H

Digital I/O GND

“L” → reset condition

-

B

Power supply for Digital core 1

“L” → Digital-out mute

“L” → Audio DAC mute

“L” → 16bit DAC mute

-

B

B

B

GND for DAC 1

-

Audio DAC Rch output 1

G

Audio DAC Lch output 1

G

Power supply for DAC 1

-

Power supply for DAC 2

-

Audio DAC Rch output 2

G

Reference voltage only for DAC G

Audio DAC Lch output 2

G

GND for DAC 2

-

PLL1 Error / LRCK output

D

PLL2 Error / BCK output

I2S audio SUB data output

D

D

No. Name

27 DATAMO

28 BCKO

29 LRCKO

30 AMCLKO

31 SPDIFO

32 DGNDIO2

33 XI

34 XO

35 DVDDIO

36 ANATEST

37 DVDDCOR2

38 DVDDREG

39 LDOPOFF

40 DGNDREG

41 LRCKI1

42 BCKI1

43 DATAI1

44 LRCKI2

45 BCKI2

46 DATAI2

47 LRCKI3

48 BCKI3

49 DATAI3

50 LRCKI4

51 BCKI4

52 DATAI4

Description of terminals

I2S audio Main data output

Type

D

I2S audio bit transfer clock output D

I2S audio LR sampling clock output D

I2S audio Synchronous clock output

D

S/PDIF output

D

Digital I/O GND 2

-

X’tal 24.576MHz input

F

X’tal 24.576MHz output

F

Digital I/O power supply

-

Analog test mode select pin

G

Power supply for Digital core 2

-

power supply for Regulator

-

Regulator POFF signal

G

GND for Regulator

I2S audio LR sampling clock input 1

I2S audio bit transfer clock input 1

I2S audio data input 1

I2S audio LR sampling clock input 2

I2S audio bit transfer clock input 2

I2S audio data input 2

I2S audio LR sampling clock input 3

I2S audio bit transfer clock input 3

I2S audio data input 3

I2S audio LR sampling clock input 4

I2S audio bit transfer clock input 4

I2S audio data input 4

-

C

C

C

C

C

C

C

C

C

C

C

C

www.rohm.com

© 2012 ROHM Co., Ltd. All rights reserved.

5/53

2012.03 - Rev.A

5 Page

BU9408KS2

Technical Note

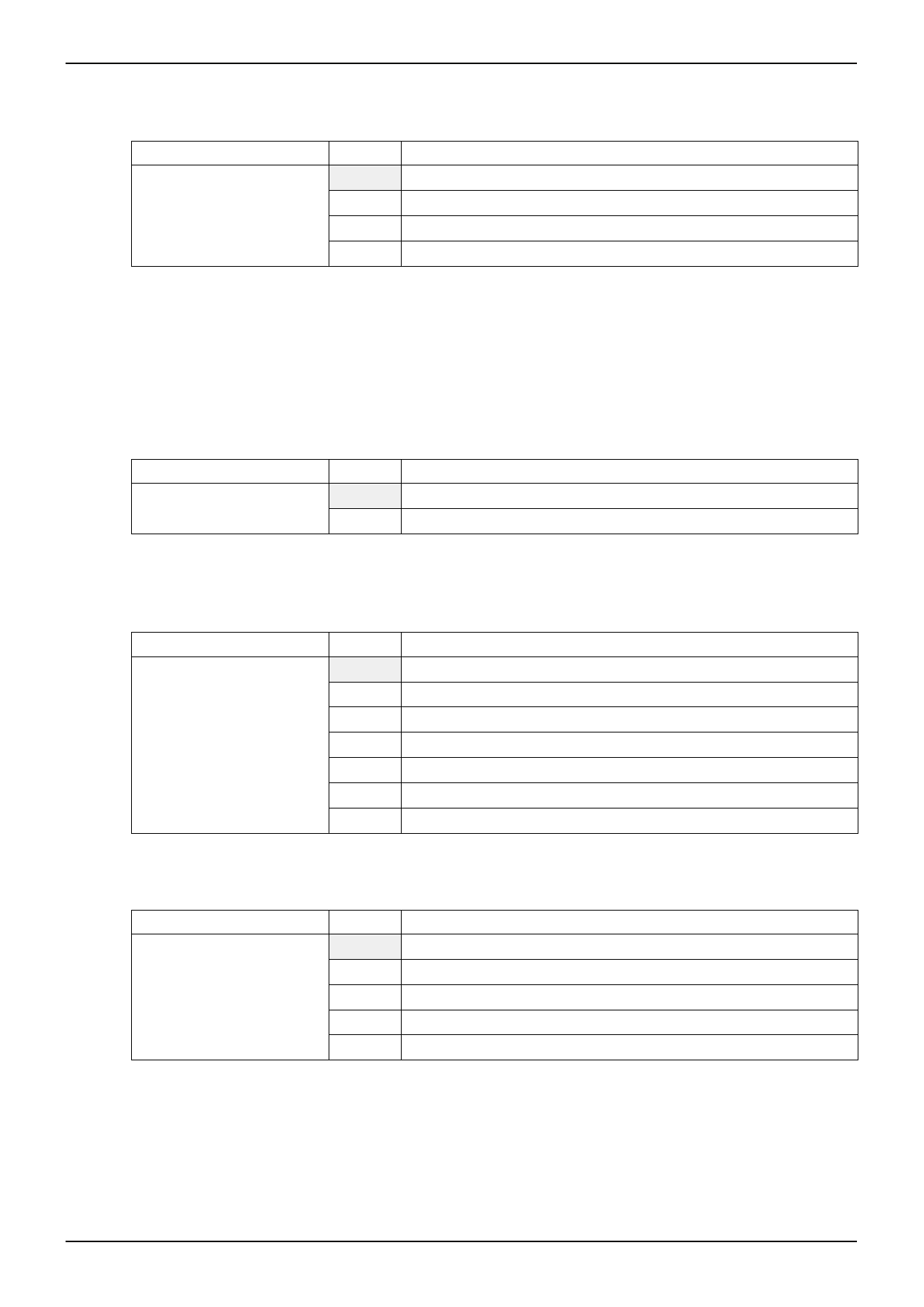

2-4. Output data selection P-S Conversion 2 for DATASO terminal (SEL2, SEL5)

Default = 0

Select Address

&h04 [ 5:4 ]

Value

0

1

2

3

Operation Description

Sub data output after DSP operation

Main data output after DSP operation

Data output before DSP operation

Data output from DF1

2-5. P-S Conversion 2 output data option (DATASO,ERR1_LRC,ERR2_BCK)

Usually, from a DATASO terminal, the result of the Sub output process of DSP is outputted to the timing (LRCKO, BCKO)

which synchronized with DATAMO.

Moreover, if this output option is set up, it will enable DATAMO to output the data of DF1 as independent data from a

DATASO terminal as a 3 line serial output with ERR1_LRC (LRCK) and ERR2_BCK (BCK).

This function is used when doing a line out output using external DAC.

Default = 0

Select Address

&h0E [ 7 ]

Value

0

Operation Description

Synchronous output with DATAMO (LRCKO, BCKO)

1 Asynchronous output with DATAMO (ERR1_LRC, ERR2_BCK)

If this function is used, the monitor of the error flag from ERROR1 and ERROR2 terminal will not be made.

2-6. Output data selecting of SPDIFO terminal (SEL1, SEL7)

Default = 0

Select Address

&h05 [ 3:0 ]

Value

0

1

2

3

4

5

6

Operation Description

Data output before DSP operation

Main data output after DSP operation

Sub data output after DSP operation

Output data from I2S_IN1 (Only data of S/PDIF form)

Output data from I2S_IN2 (Only data of S/PDIF form)

Output data from I2S_IN3 (Only data of S/PDIF form)

Output data from I2S_IN4 (Only data of S/PDIF form)

2-7. Output data selecting DF1+ΔΣDAC (SEL3)

Default = 0

Select Address

&h06 [ 2:0 ]

Value

0

1

2

3

4

Operation Description

Output data from S-P conversion 1 (Refer to &h03 [5:4])

Output data from S-P conversion 2 (Refer to &h03 [1:0])

Data output before DSP operation

Main data output after DSP operation

Sub data output after DSP operation

www.rohm.com

© 2012 ROHM Co., Ltd. All rights reserved.

11/53

2012.03 - Rev.A

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet BU9408KS2.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| BU9408KS2 | 32bit Audio DSP | ROHM Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |