|

|

PDF K4S643232H-UC-L50 Data sheet ( Hoja de datos )

| Número de pieza | K4S643232H-UC-L50 | |

| Descripción | 2M x 32 SDRAM | |

| Fabricantes | Samsung | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de K4S643232H-UC-L50 (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

K4S643232H

SDRAM

2M x 32 SDRAM

86 TSOP-II with Pb-Free

(RoHS compliant)

Revision 1.2

April 2006

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS,

AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE,

EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL

INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar

applications where Product failure could result in loss of life or personal or physical harm, or any military or

defense application, or any governmental procurement to which special terms or provisions may apply.

* Samsung Electronics reserves the right to change products or specification without notice.

- 1 - Rev. 1.2 April 2006

1 page

K4S643232H

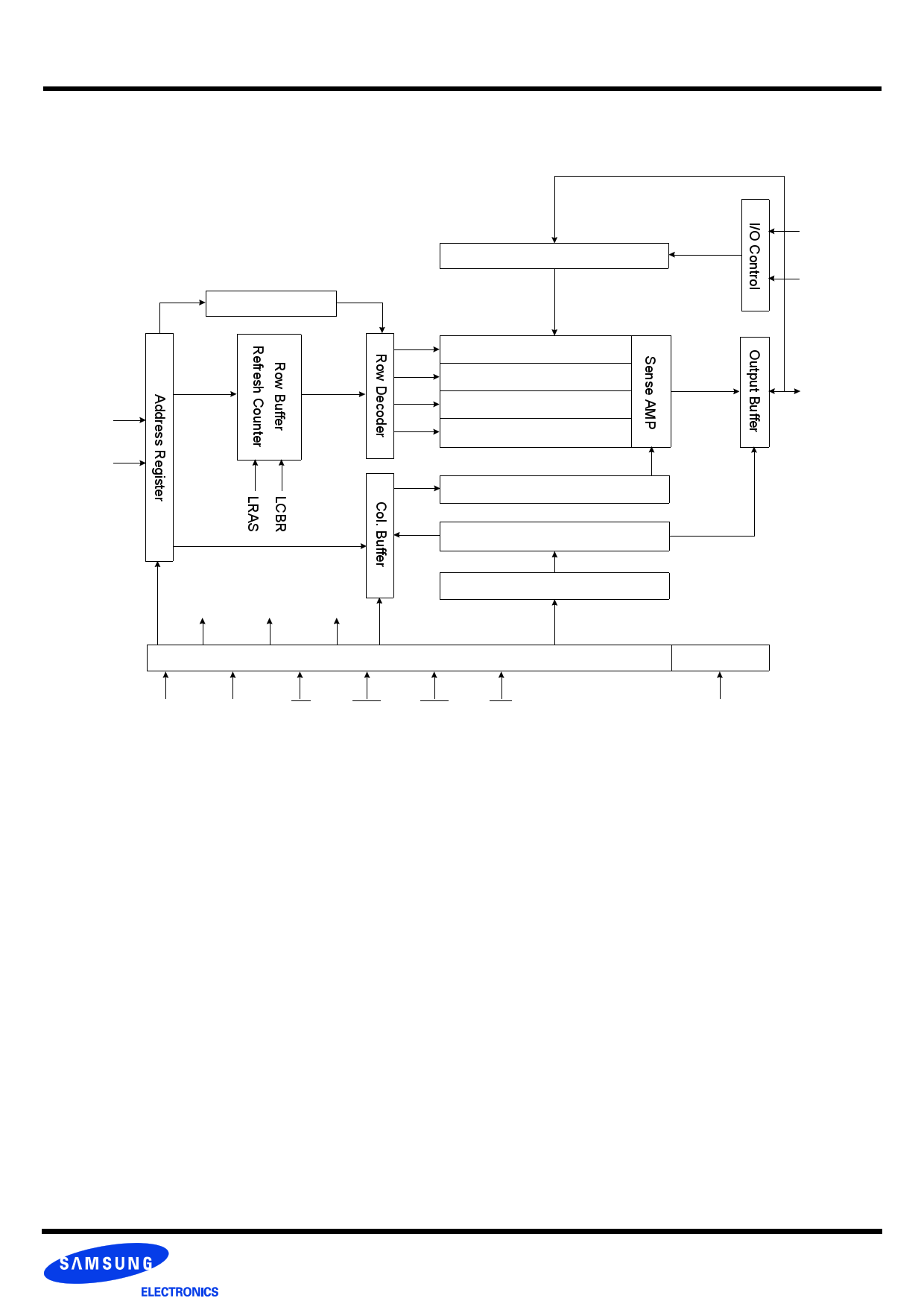

FUNCTIONAL BLOCK DIAGRAM

SDRAM

Data Input Register

CLK

ADD

Bank Select

512K x 32

512K x 32

512K x 32

512K x 32

Column Decoder

LCKE

LRAS LCBR

LWE

LCAS

Latency & Burst Length

Programming Register

LWCBR

Timing Register

CLK CKE

CS

RAS

CAS

WE

LWE

LDQM

DQi

DQM

- 5 - Rev. 1.2 April 2006

5 Page

K4S643232H

SDRAM

AC CHARACTERISTICS (AC operating conditions unless otherwise noted)

Parameter

Symbol

CLK cycle time

CLK to valid

output delay

CAS Latency=3

CAS Latency=2

CAS Latency=3

CAS Latency=2

tCC

tSAC

-50

Min Max

5

1000

10

- 4.5

-6

-55

Min Max

5.5

1000

10

- 5.0

-6

-60

Min Max

6

1000

10

- 5.5

-6

Output data hold time

tOH 2 - 2 - 2 -

CLK high pulse

width

CAS Latency=3

CAS Latency=2

tCH

2

3

-

-

2

3

- 2.5 -

-3-

CLK low

pulse width

CAS Latency=3

2 - 2 - 2.5 -

tCL

CAS Latency=2

3-3-3-

CAS Latency=3

1.5 - 1.5 - 1.5 -

Input setup time

CAS Latency=2

tSS

2.5

-

2.5

-

2.5

-

Input hold time

tSH 1 - 1 - 1 -

CLK to output in Low-Z

tSLZ

1

-

1

-

1

-

CLK to output

in Hi-Z

CAS latency=3

- 4.5 - 5.0 - 5.5

tSHZ

CAS latency=2

-6-6-6

Note : 1. Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

3. Assumed input rise and fall time (tr & tf)=1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered,

i.e., [(tr + tf)/2-1]ns should be added to the parameter.

-70

Unit Note

Min Max

7

1000 ns

10

1

- 5.5

ns 1, 2

-6

2 - ns 2

3-

ns 3

3-

3-

ns 3

3-

1.75 -

ns 3

2.5 -

1 - ns 3

1 - ns 2

- 5.5

ns -

-6

- 11 Rev. 1.2 April 2006

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet K4S643232H-UC-L50.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K4S643232H-UC-L50 | 2M x 32 SDRAM | Samsung |

| K4S643232H-UC-L55 | 2M x 32 SDRAM | Samsung |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |