|

|

PDF AD6905 Data sheet ( Hoja de datos )

| Número de pieza | AD6905 | |

| Descripción | Baseband Processor for TD-HSDPA TD-SCDMA and GSM/GPRS/EGPRS | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD6905 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

a

Baseband Processor for TD-HSDPA

TD-SCDMA and GSM/GPRS/EGPRS

Handsets and Data Modems

Preliminary Technical Data

AD6905

INTRODUCTION

The AD6905 is an advanced, low power baseband processor that

meets the demanding requirements of TD-HSDPA and

GSM/GPRS/EGPRS terminals with advanced system power

management and multimedia capabilities. The chip integrates a

powerful Blackfin® DSP processor along with an ARM926EJ-

S® microcontroller and an extensive set of peripheral interfaces

that support features such as a digital camera sensor, USB OTG,

Multimedia Card, SD (Secure Digital) Card, IrDA, thumbwheel,

color displays, and other peripheral devices such as Bluetooth,

WiLAN, and A-GPS modules.

With integrated 3G/TDD hardware acceleration to support High

Speed Downlink Packet Access (TD-HSDPA) at data rates up to

2.8Mbps, the AD6905 enables new levels of wireless

connectivity.

FEATURES

MCU Control Processor Subsystem

32-bit ARM926EJ-S® MCU Control Processor

260 MHz operation at 1.5V

16KB instruction cache

16KB data cache

4kB Instruction Tightly Coupled Memory (TCM)

2-Mbit On-chip System SRAM

Ciphering coprocessor supporting GEA1 and GEA2 and GEA3

encryption algorithms

Dedicated multi-channel DMA controller

DSP Subsystem

Blackfin 16-bit fixed-point DSP Processor

260 MHz operation at 1.5V

Memory:

L1 program space: 64 kB SRAM and 16 kB configurable

as instruction cache or SRAM

L1 data space: Two banks of 16K bytes, each with 8K

bytes of dedicated SRAM and an additional 8K bytes

that can be configured as either cache or SRAM

L2 space: 64KB SRAM

Ciphering coprocessor supporting A5/1, A5/2, A5/3, GEA1,

GEA2, GEA3, f8 and f9 ciphering algorithms

Dedicated multi-channel DMA controller

Hardware acceleration for TD-SCDMA 384kbps

and TD-HSDPA up to 2.8Mbps

Peripherals Subsystem

Support for Burst-mode, Page-mode, and NAND Flash memory

Support for SRAM, SDRAM, and PSRAM (CellularRAM)

Full-Speed USB 2.0 Dual-Role Interface with On-The-Go

(OTG) Host Mode or traditional Peripheral-only mode

Serial Display Interface

8x8 Keypad Interface

Thumbwheel Interface

4 Independent Programmable Backlights plus a Service Light

1.8V and 3.0V, 64 kbps USIM Interface

Universal System Connector Interface

Multimedia Card (MMC) Interface

Secure Digital (SD) Card Interface and SDIO

IrDA transceiver interfaces, including Fast IrDA (4 Mbps baud)

2 Configurable Generic Serial Ports (GSPs)

7 Configurable Enhanced Generic Serial Ports (eGSPs)

Applications Subsystem for Enhanced Multimedia

Parallel Peripheral Interface (PPI) for 10-bit dedicated camera

sensor or video input interface (including ITU-656 and ITU-

601 digital video)

Separate parallel bus interface for LCD displays or other

peripherals

Dedicated multi-channel 2-D DMA controller

Other Features

Real-Time Clock (RTC) with Alarm

Four General-Purpose Timers

Dedicated Interfaces to Audio/Baseband Codec Chip

Compatible with Othello® radio subsystem

Highly configurable interrupt controller architecture

Programmable bus arbitration to optimize system performance

Supports 13MHz and 26 MHz Input Clocks

Programmable Power Management and Clock Management

Slow Clocking Scheme for Low Idle Mode Current

Power Down modes

Dynamic Core Voltage Scaling from 1.1 - 1.5V

Independent I/O Voltage Domains

Embedded Trace Macrocell for MCU Debug

JTAG Interface for Test and In-Circuit Emulation of both the

MCU and DSP

Advanced features for security

Boot directly from NAND

APPLICATIONS

Dual-Mode TD-SCDMA HSDPA (voice + 2.8Mbps data) and

GSM/GPRS/EGPRS handsets (Class 12 Multi-slot EDGE)

Single or Dual-Mode TD-HSDPA wireless data modems

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices

assumes no obligation regarding future manufacture unless otherwise agreed to in writing. No responsibility is assumed by Analog Devices for its use;

nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under

any patent or patent rights of Analog Devices.

REV. PrB November 17, 2007

- 1 - ADI Proprietary & Confidential Information

1 page

Preliminary

AD6905

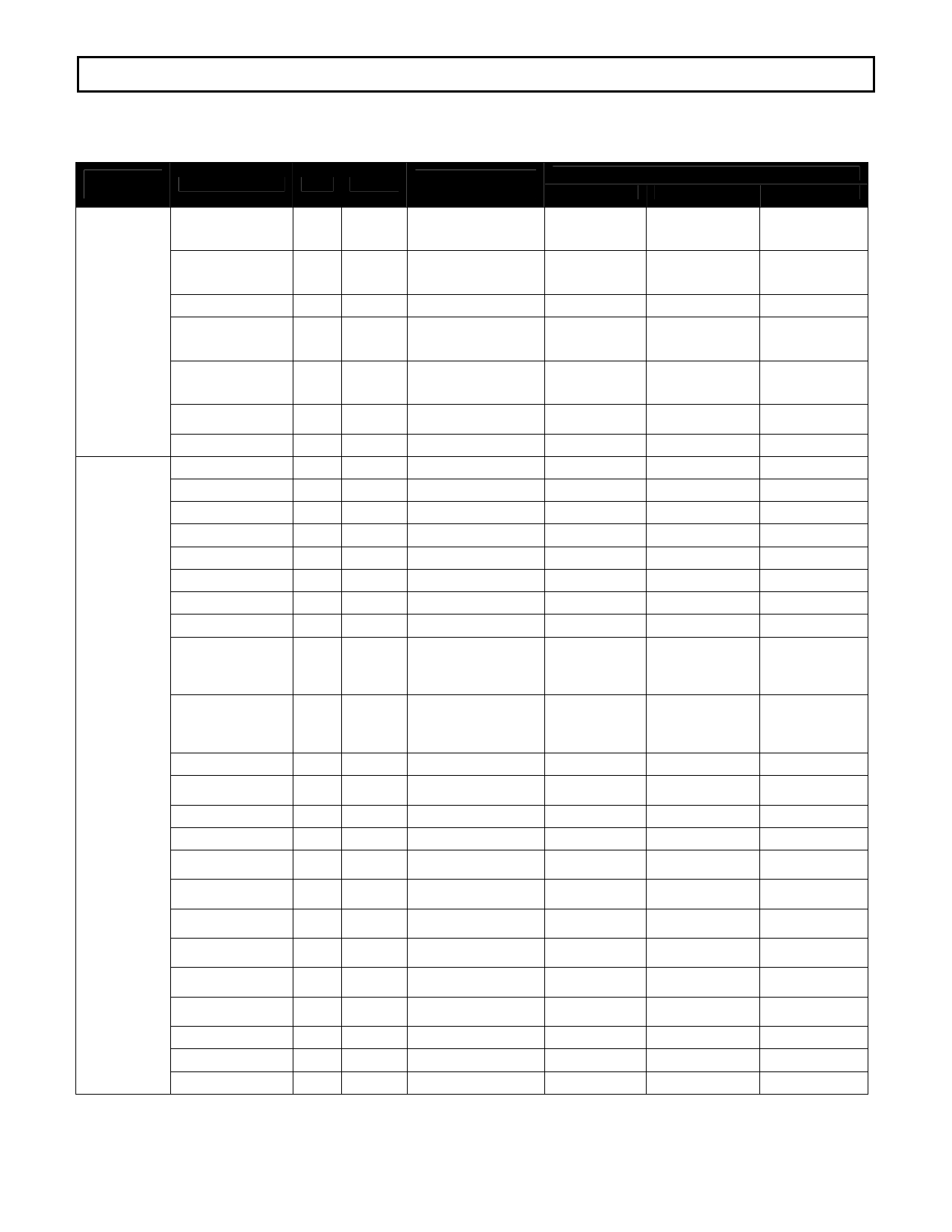

PIN MUXING TABLE

Functional

Group

Pin Name (Reset) {I/O} Supply

Default/Typical

Usage

Alternate Functions

Alt 1

Alt 2

Alt 3

CONTROL

CLKIN

CLKON (H)

nRESET

OSCIN

EBUS

External

Memory

Interface

OSCOUT (n/a)

PWRON(L)

TESTMODE

GPIO_24 (L)

GPIO_32 (L)

ADD[23] (L)

I VPLL

O VEXT

I VMEM

I VRTC

O VRTC

O VRTC

I VMEM

I/O VMEM

I/O VMEM

O VMEM

13 MHz or 26 MHz

XTAL System Clock

Input

Oscillator Power

Control Signal

(on/off)

System Reset Input

32.768 kHz Crystal

Input - Inverted (GND

if no Crystal)

32.768 kHz Oscillator

Output and Feedback

to Crystal

Power ON/OFF

Control

Must be tied to GND

Address - 32M words

Address - 16M words

Address - 8M words

ADD[25]

ADD[24]

GPIO_39

CLKMUXOUT2

ADD[22:1] (L)

O VMEM Address Bus

ADD[0] (L)

DATA[15:8] (L)

DATA[7:0] (L)

O VMEM

I/O VMEM

I/O VMEM

Display_A0

Data Bus

Data Bus

GPIO_40

nRD (H)

nHWR / nUBS /

CLE / SDQM[1]

(H)

nLWR / nLBS /

ALE / SDQM[0]

(H)

nWE (H)

nWAIT

nADV (H)

O

O

O

O

I

O

VMEM

VMEM

VMEM

VMEM

VMEM

VMEM

Read Enable

High Write Strobe /

Byte Strobe /

Command Latch

Enable / Data Mask

Low Write Strobe /

Byte Strobe /

Address Latch

Enable / Data Mask

Write Enable

External device wait

request

Valid Address (burst)

GPIO_41

GPIO_42

GPIO_43

GPIO_44

BURSTCLK (H)

nA0CS (H)

nA1CS (H)

nA2CS (H)

nA3CS (H)

GPIO_49 (I+)

GPIO_50 (I+)

GPIO_51 (I+)

O VMEM

O VMEM

O VMEM

O VMEM

O VMEM

I/O VMEM

I/O VMEM

I/O VMEM

Burst Clock

General Purpose

Chip Select

General Purpose

Chip Select

General Purpose

Chip Select

General Purpose

Chip Select

General Purpose

Chip Select

General Purpose

Chip Select

GPIO_45

GPIO_46

GPIO_47

GPIO_48

nB0CS

nB1CS

SDQM[1]

GPIO_52 (I+)

I/O VMEM

Flash 2 Chip Select nA5CS

GPIO_53 (I+)

I/O VMEM

Flash 3 Chip Select nA4CS

CLKMUXOUT2

This Information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices

assumes no obligation regarding future manufacture unless otherwise agreed to in writing. No responsibility is assumed by Analog Devices for its use;

nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under

any patent or patent rights of Analog Devices.

REV. PrB November 17, 2007

-5-

ADI Proprietary Information

5 Page

Preliminary

ARCHITECTURE OVERVIEW

The digital baseband architecture supports two processing cores:

the ARM926EJ microcontroller from ARM Ltd., (referred to as

the MCU), and Analog Devices’ Blackfin DSP processor

(referred to as the DSP). The two processors both have shared

access to all peripherals and memory subsystems through a

unified system address map, and unified system interrupt maps.

Unlike conventional DSP architectures, the Blackfin DSP

architecture supports a flexible microcontroller instruction set,

including a byte-addressed memory map. This feature, along

with a common (unified) memory map between the DSP and the

MCU (excluding control registers local to each processor), and a

flexible interrupt controller which allows any system interrupt to

be mapped to either processor, greatly simplifies the

programming model for a heterogeneous multiprocessor system.

Software tasks can easily migrate to either processor, to simplify

load balancing as the software evolves over time. In particular,

the AD6905 is specifically designed to accommodate as much of

the protocol stack as possible on the DSP, leaving the MCU free

for other applications.

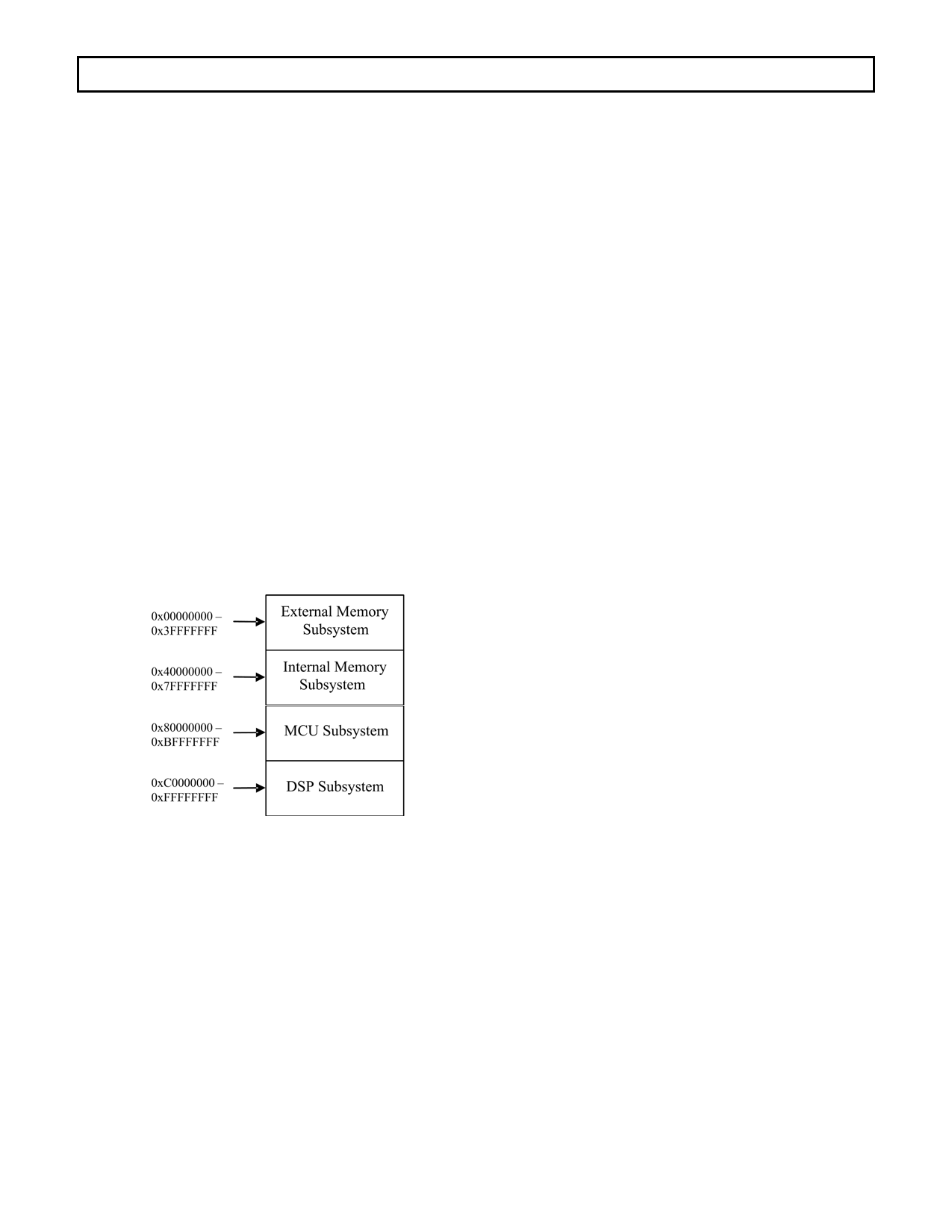

All system resources in the AD6905 are memory mapped. The

flat, 32-bit byte-address memory map of the AD6905 is

comprised of four main subsystems, as shown in the following

diagram:

Figure 2: AD6905 Shared Memory Map

The AD6905 has three DMA controllers to relieve the MCU and

DSP from repetitive operations, such as servicing I/O devices

and performing transfers from one memory block to another. In

addition to the DSP DMA controller and MCU (System) DMA

controller, the Applications subsystem has its own dedicated

DMA controller. These DMA controllers are shared resources,

AD6905

although typically the DSP programs the DSP DMA while the

MCU programs the System DMA and Applications DMA.

The two processor subsystems each have their own dedicated

interrupt controllers, JTAG TAP controllers, ciphering units, and

local control/status registers.

The internal logic, analog PLL, RTC, and the periphery I/O can

each be driven off separate power supplies, allowing for simple

I/O interfacing while minimizing core power consumption.

Level-shifting logic at each of these interfaces ensures valid

communication between each power domain, and prevents

excess current flow between the domains. The level-shifting

logic also minimizes current flow between the domains when

voltage to one of the power domains is disabled.

As the internal logic voltage is increased, control software is

able to increase the MCU and DSP clock frequencies, providing

more processing capability (i.e. MIPs). These frequencies are

produced by a single analog PLL, which multiplies to a

programmable output frequency. This signal is divided to obtain

the desired DSP clock frequency, MCU clock frequency, and

other internal synchronous clocks.

The AD6905 device interfaces to an AD6857 mixed-signal

Analog Baseband Codec (ABB), which performs the ADC/DAC

and filtering for the speech channel (microphone, speaker), as

well as the modulation and demodulation for the up- and

downlinks of the communications channel. An auxiliary

interface supports additional ADC for functions such as battery

and temperature monitoring, and the power management control

communication. For the other system components, additional

flexibility is provided in the signaling to support a wider range

of components, including large memory systems and accessory

devices.

A development bond-out package will be available to support

more extensive debug and emulation facilities, but significant

support is maintained in the production package via the JTAG

port and the Universal System Connector. This includes

hardware signal monitoring, high-throughput data and

instruction trace logging, and serial port (Voice data, I/Q data,

Messaging) access, as well as emulation of the MCU and DSP

processing cores.

The JTAG port available in the production bond-out package is

fully IEEE-compatible, and can be used to support full

boundary-scan PCB testing. Note that the boundary scan

function can be disabled, to prevent unauthorized

reprogramming of the FLASH memory via this interface. This

port also supports debug and emulation control of both the MCU

and DSP cores.

This Information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices

assumes no obligation regarding future manufacture unless otherwise agreed to in writing. No responsibility is assumed by Analog Devices for its use;

nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under

any patent or patent rights of Analog Devices.

REV. PrB November 17, 2007

- 11 -

ADI Proprietary Information

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AD6905.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD6905 | Baseband Processor for TD-HSDPA TD-SCDMA and GSM/GPRS/EGPRS | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |